Hello,

we are developing a custom platform with a main TDA4 SoC.

Processor SDK version: ti-processor-sdk-linux-j7-evm-08_06_01_02

On our platform we have connected several Marvell 88E1512 Ethernet PHY to Ethernet switch CPSW0 on main domain.

We encountered the following problem:CPSW0 eth1 cannot link up.

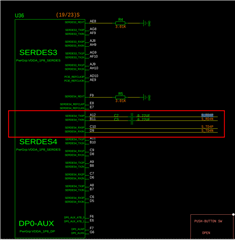

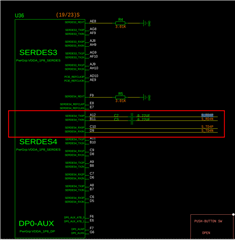

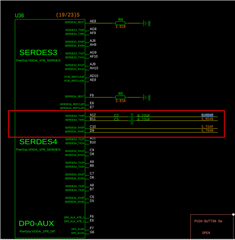

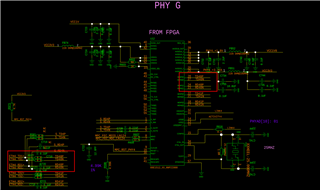

CPSW0:serdes4_sgmii_port5--->eth1

This is the hardware schematic:

dts:

arch/arm64/boot/dts/ti/k3-j721e-main.dtsi

serdes_wiz4: wiz@5050000 {

compatible = "ti,j721e-wiz-10g";

#address-cells = <1>;

#size-cells = <1>;

power-domains = <&k3_pds 297 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 297 1>, <&k3_clks 297 9>, <&cmn_refclk>;

clock-names = "fck", "core_ref_clk", "ext_ref_clk";

assigned-clocks = <&k3_clks 297 9>;

assigned-clock-parents = <&k3_clks 297 13>;

num-lanes = <4>;

#reset-cells = <1>;

ranges = <0x5050000 0x0 0x5050000 0x10000>,

<0xa030a00 0x0 0xa030a00 0x40>;

wiz4_pll0_refclk: pll0-refclk {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_pll0_refclk";

#clock-cells = <0>;

assigned-clocks = <&wiz4_pll0_refclk>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_pll1_refclk: pll1-refclk {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_pll1_refclk";

#clock-cells = <0>;

assigned-clocks = <&wiz4_pll1_refclk>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_refclk_dig: refclk-dig {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_refclk_dig";

#clock-cells = <0>;

assigned-clocks = <&wiz4_refclk_dig>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_cmn_refclk_dig_div: cmn-refclk-dig-div {

clocks = <&wiz4_refclk_dig>;

#clock-cells = <0>;

};

wiz4_cmn_refclk1_dig_div: cmn-refclk1-dig-div {

clocks = <&wiz4_pll1_refclk>;

#clock-cells = <0>;

};

serdes4: serdes@5050000 {

/*

* Note: we also map DPTX PHY registers as the Torrent

* needs to manage those.

*/

compatible = "ti,j721e-serdes-10g";

reg = <0x5050000 0x10000>,

<0xa030a00 0x40>; /* DPTX PHY */

reg-names = "torrent_phy", "dptx_phy";

resets = <&serdes_wiz4 0>;

reset-names = "torrent_reset";

clocks = <&wiz4_pll0_refclk>;

clock-names = "refclk";

#address-cells = <1>;

#size-cells = <0>;

/*

torrent_phy_dp: phy@0 {

reg = <0>;

resets = <&serdes_wiz4 1>;

cdns,phy-type = <PHY_TYPE_DP>;

cdns,num-lanes = <4>;

cdns,max-bit-rate = <5400>;

#phy-cells = <0>;

};

*/

serdes4_sgmii_link: phy@0 {

reg = <0>;

resets = <&serdes_wiz4 1>, <&serdes_wiz4 2>, <&serdes_wiz4 3>, <&serdes_wiz4 4>;

cdns,phy-type = <PHY_TYPE_SGMII>;

cdns,num-lanes = <4>;

#phy-cells = <0>;

};

};

};

arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

&serdes_ln_ctrl {

idle-states = <J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_IP4_UNUSED>,

<J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANE0_IP1_UNUSED>, <J721E_SERDES2_LANE1_USB3_1>,

<J721E_SERDES3_LANE0_USB3_0_SWAP>, <J721E_SERDES3_LANE1_USB3_0>,

<J721E_SERDES4_LANE0_QSGMII_LANE5>, <J721E_SERDES4_LANE1_QSGMII_LANE6>,

<J721E_SERDES4_LANE2_QSGMII_LANE7>, <J721E_SERDES4_LANE3_QSGMII_LANE8>;

};

mdio_pins_default: mdio-pins-default {

pinctrl-single,pins = <

J721E_IOPAD(0x1bc, PIN_OUTPUT, 0) /* (V24) MDIO0_MDC */

J721E_IOPAD(0x1b8, PIN_INPUT, 0) /* (V26) MDIO0_MDIO */

>;

};

rgmii3_pins_default: rgmii3-pins-default {

pinctrl-single,pins = <

J721E_IOPAD(0xb0, PIN_INPUT, 4) /* (AF28) PRG0_PRU0_GPO0.RGMII3_RD0 */

J721E_IOPAD(0xb4, PIN_INPUT, 4) /* (AE28) PRG0_PRU0_GPO1.RGMII3_RD1 */

J721E_IOPAD(0xb8, PIN_INPUT, 4) /* (AE27) PRG0_PRU0_GPO2.RGMII3_RD2 */

J721E_IOPAD(0xbc, PIN_INPUT, 4) /* (AD26) PRG0_PRU0_GPO3.RGMII3_RD3 */

J721E_IOPAD(0xc8, PIN_INPUT, 4) /* (AE26) PRG0_PRU0_GPO6.RGMII3_RXC */

J721E_IOPAD(0xc0, PIN_INPUT, 4) /* (AD25) PRG0_PRU0_GPO4.RGMII3_RX_CTL */

J721E_IOPAD(0xdc, PIN_OUTPUT, 4) /* (AJ28) PRG0_PRU0_GPO11.RGMII3_TD0 */

J721E_IOPAD(0xe0, PIN_OUTPUT, 4) /* (AH27) PRG0_PRU0_GPO12.RGMII3_TD1 */

J721E_IOPAD(0xe4, PIN_OUTPUT, 4) /* (AH29) PRG0_PRU0_GPO13.RGMII3_TD2 */

J721E_IOPAD(0xe8, PIN_OUTPUT, 4) /* (AG28) PRG0_PRU0_GPO14.RGMII3_TD3 */

J721E_IOPAD(0xf0, PIN_OUTPUT, 4) /* (AH28) PRG0_PRU0_GPO16.RGMII3_TXC */

J721E_IOPAD(0xec, PIN_OUTPUT, 4) /* (AG27) PRG0_PRU0_GPO15.RGMII3_TX_CTL */

>;

};

rgmii8_pins_default: rgmii8-default-pins {

pinctrl-single,pins = <

J721E_IOPAD(0x58, PIN_INPUT, 8) /* (AE22) PRG1_PRU1_GPO0.RGMII8_RD0 */

J721E_IOPAD(0x5c, PIN_INPUT, 8) /* (AG23) PRG1_PRU1_GPO1.RGMII8_RD1 */

J721E_IOPAD(0x60, PIN_INPUT, 8) /* (AF23) PRG1_PRU1_GPO2.RGMII8_RD2 */

J721E_IOPAD(0x64, PIN_INPUT, 8) /* (AD23) PRG1_PRU1_GPO3.RGMII8_RD3 */

J721E_IOPAD(0x70, PIN_INPUT, 8) /* (AE23) PRG1_PRU1_GPO6.RGMII8_RXC */

J721E_IOPAD(0x68, PIN_INPUT, 8) /* (AH24) PRG1_PRU1_GPO4.RGMII8_RX_CTL */

J721E_IOPAD(0x84, PIN_OUTPUT, 8) /* (AJ25) PRG1_PRU1_GPO11.RGMII8_TD0 */

J721E_IOPAD(0x88, PIN_OUTPUT, 8) /* (AH25) PRG1_PRU1_GPO12.RGMII8_TD1 */

J721E_IOPAD(0x8c, PIN_OUTPUT, 8) /* (AG25) PRG1_PRU1_GPO13.RGMII8_TD2 */

J721E_IOPAD(0x90, PIN_OUTPUT, 8) /* (AH26) PRG1_PRU1_GPO14.RGMII8_TD3 */

J721E_IOPAD(0x98, PIN_OUTPUT, 8) /* (AJ26) PRG1_PRU1_GPO16.RGMII8_TXC */

J721E_IOPAD(0x94, PIN_OUTPUT, 8) /* (AJ27) PRG1_PRU1_GPO15.RGMII8_TX_CTL */

>;

};

&cpsw0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&mdio_pins_default

&rgmii3_pins_default

&rgmii8_pins_default>;

};

&cpsw0_port1 {

status = "disabled";

};

&cpsw0_port2 {

status = "disabled";

};

&cpsw0_port3 {

status = "okay";

phy-handle = <&cpsw9g_phy0>;

phy-mode = "rgmii-rxid";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 3>;

};

&cpsw0_port4 {

status = "disabled";

};

&cpsw0_port5 {

status = "okay";

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 5>, <&serdes4_sgmii_link>;

phy-names = "portmode", "serdes-phy";

phy-handle = <&cpsw9g_phy2>;

};

&cpsw0_port6 {

status = "disabled";

};

&cpsw0_port7 {

status = "disabled";

};

&cpsw0_port8 {

status = "okay";

phy-handle = <&cpsw9g_phy1>;

phy-mode = "rgmii-rxid";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 8>;

};

&cpsw9g_mdio {

bus_freq = <1000000>;

#address-cells = <1>;

#size-cells = <0>;

cpsw9g_phy0: ethernet-phy@0 {

status = "okay";

reg = <0>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

ti,min-output-impedance;

};

cpsw9g_phy1: ethernet-phy@1 {

status = "okay";

reg = <1>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

ti,min-output-impedance;

};

cpsw9g_phy2: ethernet-phy@2 {

status = "okay";

reg = <2>;

//ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

//ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

//ti,min-output-impedance;

};

};

&main_r5fss0_core0 {

firmware-name = "pdk-ipc/ipc_echo_test_mcu2_0_release_strip.xer5f";

};

boot log:

root@tda4vm-sk:~# dmesg | grep mdio

[ 1.456167] davinci_mdio 46000f00.mdio: Configuring MDIO in manual mode

[ 1.499085] davinci_mdio 46000f00.mdio: davinci mdio revision 9.7, bus freq 1000000

[ 1.514050] davinci_mdio 46000f00.mdio: phy[1]: device 46000f00.mdio:01, driver Marvell 88E1510

[ 1.559439] davinci_mdio c000f00.mdio: Configuring MDIO in manual mode

[ 1.603084] davinci_mdio c000f00.mdio: davinci mdio revision 9.7, bus freq 1000000

[ 1.618255] mdio_bus c000f00.mdio: MDIO device at address 1 is missing.

[ 1.625174] mdio_bus c000f00.mdio: MDIO device at address 2 is missing.

[ 1.631772] davinci_mdio c000f00.mdio: phy[0]: device c000f00.mdio:00, driver Marvell 88E1510

[ 4.307770] davinci_mdio 46000f00.mdio: Configuring MDIO in manual mode

[ 4.351092] davinci_mdio 46000f00.mdio: davinci mdio revision 9.7, bus freq 1000000

[ 4.366013] davinci_mdio 46000f00.mdio: phy[1]: device 46000f00.mdio:01, driver Marvell 88E1510

[ 4.419867] davinci_mdio c000f00.mdio: Configuring MDIO in manual mode

[ 4.463092] davinci_mdio c000f00.mdio: davinci mdio revision 9.7, bus freq 1000000

[ 4.478248] mdio_bus c000f00.mdio: MDIO device at address 1 is missing.

[ 4.485167] mdio_bus c000f00.mdio: MDIO device at address 2 is missing.

[ 4.491766] davinci_mdio c000f00.mdio: phy[0]: device c000f00.mdio:00, driver Marvell 88E1510

[ 12.891371] am65-cpsw-nuss c000000.ethernet eth1: PHY [c000f00.mdio:00] driver [Marvell 88E1510] (irq=POLL)

[ 12.996884] am65-cpsw-nuss 46000000.ethernet eth0: PHY [46000f00.mdio:01] driver [Marvell 88E1510] (irq=POLL)

root@tda4vm-sk:~# dmesg | grep ethernet

[ 1.522780] am65-cpsw-nuss 46000000.ethernet: initializing am65 cpsw nuss version 0x6BA00101, cpsw version 0x6BA80100 Ports: 2 quirks:00000000

[ 1.535582] am65-cpsw-nuss 46000000.ethernet: initialized cpsw ale version 1.4

[ 1.542787] am65-cpsw-nuss 46000000.ethernet: ALE Table size 64

[ 1.549086] am65-cpsw-nuss 46000000.ethernet: CPTS ver 0x4e8a010a, freq:500000000, add_val:1 pps:0

[ 1.640322] am65-cpsw-nuss c000000.ethernet: initializing am65 cpsw nuss version 0x6BA01901, cpsw version 0x6BA80101 Ports: 9 quirks:00000000

[ 1.653088] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 1.660516] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 1.666838] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 1.673103] am65-cpsw-nuss c000000.ethernet: initialized cpsw ale version 1.4

[ 1.680221] am65-cpsw-nuss c000000.ethernet: ALE Table size 512

[ 1.686524] am65-cpsw-nuss c000000.ethernet: CPTS ver 0x4e8a010a, freq:200000000, add_val:4 pps:0

[ 4.374741] am65-cpsw-nuss 46000000.ethernet: initializing am65 cpsw nuss version 0x6BA00101, cpsw version 0x6BA80100 Ports: 2 quirks:00000000

[ 4.387542] am65-cpsw-nuss 46000000.ethernet: initialized cpsw ale version 1.4

[ 4.394749] am65-cpsw-nuss 46000000.ethernet: ALE Table size 64

[ 4.401026] am65-cpsw-nuss 46000000.ethernet: CPTS ver 0x4e8a010a, freq:500000000, add_val:1 pps:0

[ 4.411362] am65-cpsw-nuss 46000000.ethernet: set new flow-id-base 48

[ 4.500318] am65-cpsw-nuss c000000.ethernet: initializing am65 cpsw nuss version 0x6BA01901, cpsw version 0x6BA80101 Ports: 9 quirks:00000000

[ 4.513083] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 4.519436] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 4.525752] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 4.532008] am65-cpsw-nuss c000000.ethernet: initialized cpsw ale version 1.4

[ 4.539126] am65-cpsw-nuss c000000.ethernet: ALE Table size 512

[ 4.545401] am65-cpsw-nuss c000000.ethernet: CPTS ver 0x4e8a010a, freq:200000000, add_val:4 pps:0

[ 4.556723] am65-cpsw-nuss c000000.ethernet: set new flow-id-base 140

[ 12.891371] am65-cpsw-nuss c000000.ethernet eth1: PHY [c000f00.mdio:00] driver [Marvell 88E1510] (irq=POLL)

[ 12.931152] am65-cpsw-nuss c000000.ethernet eth1: configuring for phy/rgmii-rxid link mode

[ 12.996884] am65-cpsw-nuss 46000000.ethernet eth0: PHY [46000f00.mdio:01] driver [Marvell 88E1510] (irq=POLL)

[ 13.023153] am65-cpsw-nuss 46000000.ethernet eth0: configuring for phy/rgmii-rxid link mode

[ 15.160101] am65-cpsw-nuss 46000000.ethernet eth0: Link is Up - 100Mbps/Full - flow control rx/tx

========================================================================================

Now, we only have TD40P, TD40N, RD40P, and RD40N cables connected to our hardware for 100Mbps use. Here is the situation with my eth1.

Please help me investigate what caused it? Thank you.