Other Parts Discussed in Thread: TDA4VH

Hi TI:

The board I'm currently using is the 9.0 SDK for TDA4VH.

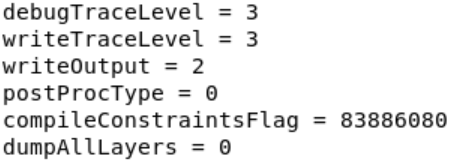

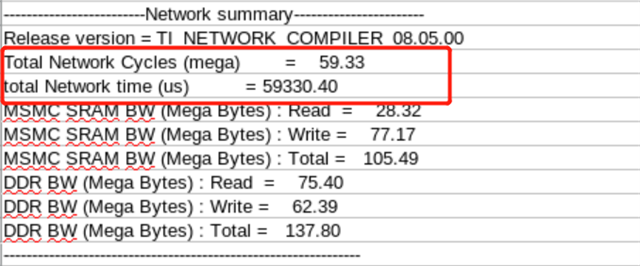

I want to export the model via the TIDL PC Importer tool to get the board-side inference time for the PC simulation, so I use the compileConstraintsFlag parameter.

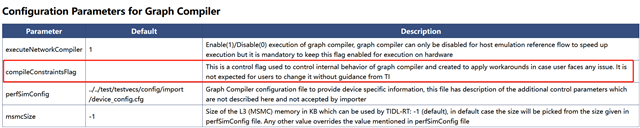

I found a description of the compileConstraintsFlag parameter in the documentation released by TI.

So, how do I configure the compileConstraintsFlag parameter when exporting the model?

Thank you