Other Parts Discussed in Thread: TDA2,

EVM board

SDK 0804

The ub960 work in line interleave mode with 4 camera , but we find all camera images combine to a single buff.

How can we separate the image from the 4 cameras into separate buffers

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Jin,

You would have to run additional DMA to separate them. There is no reference example in SDK to separate them.

Regards,

Brijesh

Hi,

In the SDK, all the demos assume that the DES sends in the data with separate virtual channel.

Hence, the SHIM layer stores the buffer in DDR based on the Virtual channel ID.

In your case, since the DDR itself has all channels interleaved as one buffer, you would require to do another dma copy to deinterleave from that buffer to another separate buffers in the DDR.

However, currently we do not have a out of the box example in the SDK that does the same.

Regards,

Nikhil

Hi Nikhil,

Can TDA2 split the interleaved image into 4 buffers without extra DMA copy ? Deinterleaving the bufffer will consume more DDR bandwidth, so ti will low the whole performance, expecially for C7X which needs more throughout. Using another DMA to deinterleave image is not a good solution, do you have other recommendation to relsove the problem?

Thank you in advance!

BR

Yunjie Li

Hi

Can TDA2 split the interleaved image into 4 buffers without extra DMA copy ?

May I know if you are referring to TDA2 or TDA4?

I assumed the thread was opened for TDA4VM.

In case of csi-rx of TDA4VM, the SHIM layer gives different UDMA PSIL thread based on a VC-DT combination.

The ub960 work in line interleave mode with 4 camera , but we find all camera images combine to a single buff.

May I know why you require to use UB960 is in this mode?

Regards,

Nikhil

I mean TDA2, the original design adopts TDA2(the solution is provided by other vendor). Now,we want to replace TDA2 with TDA4, so I have to follow the legacy the requirement of peer. I have no idea weather TDA2 can deinterleave the image, do you know the relevant implement of TDA2 ?

BR

Yunjie Li

Hi Li,

Do you mean TDA2Px? Because TDA2x doesnot support MIPI input and TDA2Px does support MIPI input via CAL module.

CAL module can separate the camera data using virtual channel and data type fields and then can store them in separate buffers. This is same as CSIRX. If it is line interleaved data, CAL and CSIRX both will store them in a same buffer and then you need to separate them using another DMA.

I am wondering where this data is processed. Is it going to be processed in the ISP?

Regards,

Brijesh

Do you mean TDA2Px?

[Yunjie Li]: yes.

I am wondering where this data is processed. Is it going to be processed in the ISP?

[Yunjie Li]: The data is processed by A72, bypass ISP, the format of data is yuv422.

We try to use UDMA 2D to deinterleave an interleaved image of 12MB( 4 streams) on MCU2_0, it takes 6ms to get an image (3MB) by triggering UDMA 2D, so 4 images will take 6ms * 4 = 24ms. During this time, other components(C66, C7x)can not access DDR, it comsumes too much resource, the CV algorithm may be not deployed, so the solution does not make sense on TDA4.

By the way, the camera is 30 fps.

BR

Yunjie Li

Hi Li,

ok, in this case, isn't it better to update CV algorithm to support this line interleaved image? CV algorithm needs to just play with the pitch and start address to get the correct image of each input camera. This will save the DDR BW and also latency..

Regards,

Brijesh

isn't it better to update CV algorithm to support this line interleaved image

It is impossible to persuade CV guys to accept it, I will try other method to avoid deinterleaving in SOC.

Thank you so much!

BR

Yunjie Li

You can probably use other HW accelerator to separate them. Like DSS M2M path can accept YUV422 and can also output YUV422, so you can use it to separate them.

Regards,

Brijesh

Hi Brijesh,

Need you help give more guide about the DSS M2M for customer. do we have some demo code for customer?

BR,

Biao

Hi Brijesh,

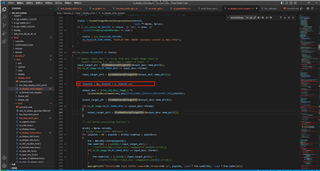

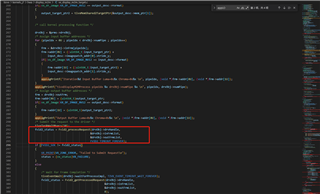

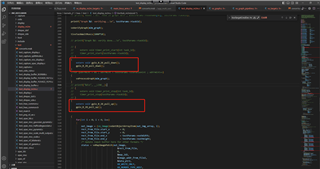

Customer have done DSS m2m to split this picture. The two source files customer modified and the generated patch file are in the attachment.

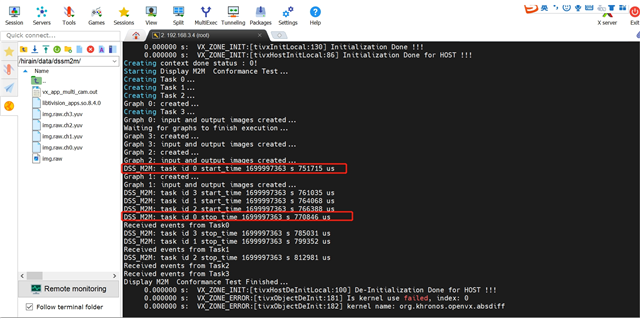

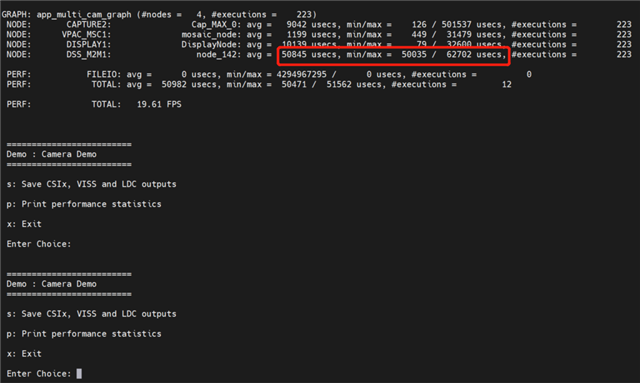

The log running locally is as follows: Currently, all four tasks are enabled and run together.

There is some running latency(around 20ms) issue, it slower than do it via MCU. Need you help to reduce the latency? In addition to the running time problem, it seems that the split image also has some problems and becomes a bit blurry. Can you help review the code?

The original large picture, the four small pictures split by python script, and the four small pictures split by DSS M2M are all in below link.

https://tidrive.ext.ti.com/u/9lFCH0tRQlfkUUIR/6a1ac96e-36ad-4d8e-be84-750c390b75f3?l

3;rrD8ZY

BR,

Biao

Hongyao, that's great to hear you make this in progress. Did you split/copy and deinterleaved those super-frame by A72 correctly, from the data integrity point of view?

BTW, at least for me, it's not surprise at all the empty 2xA72 can do this memcpy better, because the frequency and performance of CPU is very high compared to all the other hardware accelerators.

appreciate.

hi Yunjie Li, hongyao jin,

Did you take care of cache operations before saving these images into a file? If not, can you check and take care of it? Buffers are typically cached mapped on all cores, so they should not be accessed without cache operation and without cache operation, the content written in the file may not be correct.

Also i did not get that small size by A72 is correct?? Do you mean the above performance data is for small size image? and do you only see these one correct?

Regards,

Brijesh

1. We don't think the cache is causing this problem, because the data in memory is actually modified before and after the M2M operation

2. yes, the two images above are channel 0, one is split by memcpy, the other is split by M2M, but the images of the four channels after splitting by M2M are completely consistent

Brijesh, kindly here we need BU urgent support to work out an example, for instance, test_display_m2m.c, in order to fulfill the deinterleaving of super frame by lines of 4x/channels.

Technically, as we aligned, the tiovx display node should be extended to support pitching of ovx image object.

appreciate.

Hi Xu,

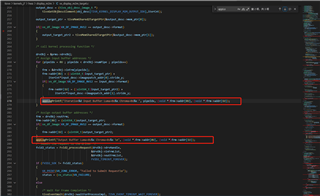

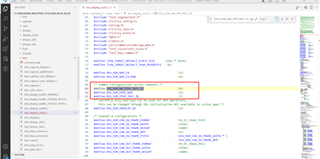

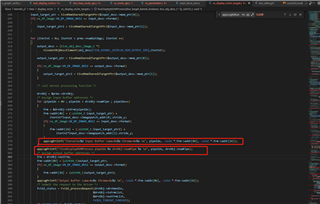

As discussed over the email, please find attached patch to add support for de-interleaving in DSS M2M node. Please apply this patch on top of ti-processor-sdk-rtos-j721e-evm-08_04_00_06/tiovx folder.

In this patch,

1, I have added additional create time parameter “enable_deiniterleave” in DSS M2M tivx_display_m2m_params_t struct.

2, when this flag is set, DSS M2M node expects input as image and output as one of the element of the object array. It expects input frame size to be ‘n’ times the output image size and image format to be same. It also expects the ‘n’ images are line interleaved in the input image exactly at the pitch boundary.

3, the input address is calculated at the pich offset and output image is extracted from the image array.

Regards,

Brijesh

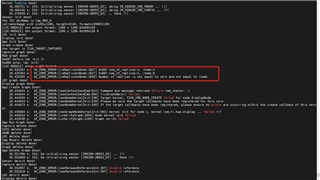

After patch was applied, it was consistent with the previous phenomenon that split images still failed, and when deinterleave was enabled, the program would be stuck

the log when deinterleave is enabled

root@p789-adcu1:~#

root@p789-adcu1:~# cd /hirain/data/ti_dss_patch/

root@p789-adcu1:/hirain/data/ti_dss_patch#

root@p789-adcu1:/hirain/data/ti_dss_patch# ./vx_app_multi_cam.out

APP: Init ... !!!

MEM: Init ... !!!

MEM: Initialized DMA HEAP (fd=4) !!!

MEM: Init ... Done !!!

IPC: Init ... !!!

IPC: Init ... Done !!!

REMOTE_SERVICE: Init ... !!!

REMOTE_SERVICE: Init ... Done !!!

0.000000 s: GTC Frequency = 0 MHz

APP: Init ... Done !!!

0.000000 s: VX_ZONE_INIT:Enabled

0.000000 s: VX_ZONE_ERROR:Enabled

0.000000 s: VX_ZONE_WARNING:Enabled

0.000000 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

0.000000 s: VX_ZONE_INIT:[tivxHostInitLocal:86] Initialization Done for HOST !!!

Creating context done status : 0!

Starting Display M2M Conformance Test...

Starting Display M2M Conformance Test 2...

0.000000 s: VX_ZONE_INFO:Enabled

Creating Task 0...

Waiting for graphs to finish execution...

Graph 0: created...

Graph 0: input and output images created...

Graph 0: input and output images created 2 ...

251

294

298

312

314

316

DSS_M2M: task id 0 start_time 1699996576 s 261890 us

0.000000 s: VX_ZONE_INFO:[ownNodeKernelValidate:241] Validating kernel com.ti.hwa.displaym2m

0.000000 s: VX_ZONE_INNOTICE:

the log when deinterleave is disabled

root@p789-adcu1:~#

root@p789-adcu1:~# cd /hirain/data/ti_dss_patch/

root@p789-adcu1:/hirain/data/ti_dss_patch#

root@p789-adcu1:/hirain/data/ti_dss_patch# ls -l

total 40304

-rw-r--r-- 1 root root 1541 Nov 15 2023 app_multi_cam.cfg

-rw-r--r-- 1 root root 13158400 Nov 15 2023 img_raw.yuv

-rw-r--r-- 1 root root 28054632 Nov 15 05:17 libtivision_apps.so.8.4.0

-rwxr-xr-x 1 root root 45720 Nov 15 05:16 vx_app_multi_cam.out

root@p789-adcu1:/hirain/data/ti_dss_patch#

root@p789-adcu1:/hirain/data/ti_dss_patch#

root@p789-adcu1:/hirain/data/ti_dss_patch# ./vx_app_multi_cam.out

APP: Init ... !!!

MEM: Init ... !!!

MEM: Initialized DMA HEAP (fd=4) !!!

MEM: Init ... Done !!!

IPC: Init ... !!!

IPC: Init ... Done !!!

REMOTE_SERVICE: Init ... !!!

REMOTE_SERVICE: Init ... Done !!!

0.000000 s: GTC Frequency = 0 MHz

APP: Init ... Done !!!

0.000000 s: VX_ZONE_INIT:Enabled

0.000000 s: VX_ZONE_ERROR:Enabled

0.000000 s: VX_ZONE_WARNING:Enabled

0.000000 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

0.000000 s: VX_ZONE_INIT:[tivxHostInitLocal:86] Initialization Done for HOST !!!

Creating context done status : 0!

Starting Display M2M Conformance Test...

Starting Display M2M Conformance Test 2...

0.000000 s: VX_ZONE_INFO:Enabled

Creating Task 0...

Waiting for graphs to finish execution...

Graph 0: created...

Graph 0: input and output images created...

Graph 0: input and output images created 2 ...

251

294

298

312

314

316

DSS_M2M: task id 0 start_time 1699996676 s 346544 us

0.000000 s: VX_ZONE_INFO:[ownNodeKernelValidate:241] Validating kernel com.ti.hwa.displaym2m

0.000000 s: VX_ZONE_INFO:[ownNodeKernelInit:523] Calling create callback for node node_91

0.000000 s: VX_ZONE_INFO:[ownNodeKernelInit:529] Create callback for node node_91 completed

0.000000 s: VX_ZONE_INFO:[ownGraphNodeKernelInit:578] kernel init for node 0, kernel com.ti.hwa.displaym2m ...

0.000000 s: VX_ZONE_INFO:[ownGraphNodeKernelInit:589] kernel init for node 0, kernel com.ti.hwa.displaym2m ... done !!!

0.000000 s: VX_ZONE_INFO:[ownGraphScheduleGraph:764] Scheduling Graph (graph=15, pipe=0)

0.000000 s: VX_ZONE_INFO:[ownNodeKernelSchedule:627] Scheduling Node (node=12, pipe=0)

0.000000 s: VX_ZONE_INFO:[ownCheckGraphCompleted:677] Graph Completed (graph=15, pipe=0)

0.000000 s: VX_ZONE_INFO:[ownCheckGraphCompleted:705] All Graphs Completed

334

DSS_M2M: task id 0 stop_time 1699996676 s 363282 us

0.000000 s: VX_ZONE_INFO:[tivxQueueDelete:182] if this hangs, please ensure all application threads have been destroyed

Received events from Task0

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.vpac_nf_generic destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.vpac_nf_bilateral destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.dmpac_sde destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.vpac_ldc destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.vpac_msc_multi_scale destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.vpac_msc_pyramid destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.dmpac_dof destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.dof_visualize destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.vpac_viss destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.display destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.capture destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.csitx destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:[ownDestructKernel:44] Kernel com.ti.hwa.displaym2m destructor called (removed from context)

0.000000 s: VX_ZONE_INFO:Enabled

Display M2M Conformance Test Finished...

0.000000 s: VX_ZONE_INIT:[tivxHostDeInitLocal:100] De-Initialization Done for HOST !!!

0.000000 s: VX_ZONE_ERROR:[tivxObjectDeInit:181] Is kernel use failed, index: 0

0.000000 s: VX_ZONE_ERROR:[tivxObjectDeInit:182] kernel name: org.khronos.openvx.absdiff

0.000000 s: VX_ZONE_ERROR:[tivxObjectDeInit:230] Is image use failed, index: 2

0.000000 s: VX_ZONE_ERROR:[tivxObjectDeInit:278] Is error use failed, index: 0

0.000000 s: VX_ZONE_INFO:[tivxQueueDelete:182] if this hangs, please ensure all application threads have been destroyed

0.000000 s: VX_ZONE_INFO:[tivxQueueDelete:182] if this hangs, please ensure all application threads have been destroyed

0.000000 s: VX_ZONE_INFO:[tivxQueueDelete:182] if this hangs, please ensure all application threads have been destroyed

0.000000 s: VX_ZONE_INFO:[tivxQueueDelete:182] if this hangs, please ensure all application threads have been destroyed

0.000000 s: VX_ZONE_INIT:[tivxDeInitLocal:193] De-Initialization Done !!!

APP: Deinit ... !!!

REMOTE_SERVICE: Deinit ... !!!

REMOTE_SERVICE: Deinit ... Done !!!

IPC: Deinit ... !!!

IPC: DeInit ... Done !!!

MEM: Deinit ... !!!

DDR_SHARED_MEM: Alloc's: 8 alloc's of 52633620 bytes

DDR_SHARED_MEM: Free's : 8 free's of 52633620 bytes

DDR_SHARED_MEM: Open's : 0 allocs of 0 bytes

DDR_SHARED_MEM: Total size: 805306368 bytes

MEM: Deinit ... Done !!!

APP: Deinit ... Done !!!

root@p789-adcu1:/hirain/data/ti_dss_patch#

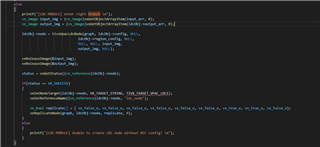

The modified source file is as follows

/*

*

* Copyright (c) 2021 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

#include "TI/tivx.h"

#include "tivx_hwa_kernels.h"

#include "tivx_kernel_display_m2m.h"

#include "TI/tivx_target_kernel.h"

static vx_kernel vx_display_m2m_kernel = NULL;

static vx_status VX_CALLBACK tivxAddKernelDisplayM2MValidate(vx_node node,

const vx_reference parameters[ ],

vx_uint32 num,

vx_meta_format metas[]);

static vx_status VX_CALLBACK tivxAddKernelDisplayM2MInitialize(vx_node node,

const vx_reference parameters[ ],

vx_uint32 num_params);

vx_status tivxAddKernelDisplayM2M(vx_context context);

vx_status tivxRemoveKernelDisplayM2M(vx_context context);

static vx_status VX_CALLBACK tivxAddKernelDisplayM2MValidate(vx_node node,

const vx_reference parameters[ ],

vx_uint32 num,

vx_meta_format metas[])

{

vx_status status = (vx_status)VX_SUCCESS;

vx_user_data_object configuration = NULL;

vx_char configuration_name[VX_MAX_REFERENCE_NAME];

vx_size configuration_size;

tivx_display_m2m_params_t params;

vx_image input = NULL;

vx_uint32 input_w;

vx_uint32 input_h;

vx_df_image input_fmt;

vx_image output = NULL;

vx_uint32 output_w;

vx_uint32 output_h;

vx_df_image output_fmt;

if ( (num != TIVX_KERNEL_DISPLAY_M2M_MAX_PARAMS)

|| (NULL == parameters[TIVX_KERNEL_DISPLAY_M2M_CONFIGURATION_IDX])

|| (NULL == parameters[TIVX_KERNEL_DISPLAY_M2M_INPUT_IDX])

|| (NULL == parameters[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX])

)

{

status = (vx_status)VX_ERROR_INVALID_PARAMETERS;

VX_PRINT(VX_ZONE_ERROR, "One or more REQUIRED parameters are set to NULL\n");

}

if ((vx_status)VX_SUCCESS == status)

{

configuration = (vx_user_data_object)parameters[TIVX_KERNEL_DISPLAY_M2M_CONFIGURATION_IDX];

input = (vx_image)parameters[TIVX_KERNEL_DISPLAY_M2M_INPUT_IDX];

output = (vx_image)parameters[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX];

}

/* PARAMETER ATTRIBUTE FETCH */

if ((vx_status)VX_SUCCESS == status)

{

tivxCheckStatus(&status, vxQueryUserDataObject(configuration, (vx_enum)VX_USER_DATA_OBJECT_NAME, &configuration_name, sizeof(configuration_name)));

tivxCheckStatus(&status, vxQueryUserDataObject(configuration, (vx_enum)VX_USER_DATA_OBJECT_SIZE, &configuration_size, sizeof(configuration_size)));

tivxCheckStatus(&status, vxQueryImage(input, (vx_enum)VX_IMAGE_WIDTH, &input_w, sizeof(input_w)));

tivxCheckStatus(&status, vxQueryImage(input, (vx_enum)VX_IMAGE_HEIGHT, &input_h, sizeof(input_h)));

tivxCheckStatus(&status, vxQueryImage(input, (vx_enum)VX_IMAGE_FORMAT, &input_fmt, sizeof(input_fmt)));

tivxCheckStatus(&status, vxQueryImage(output, (vx_enum)VX_IMAGE_WIDTH, &output_w, sizeof(output_w)));

tivxCheckStatus(&status, vxQueryImage(output, (vx_enum)VX_IMAGE_HEIGHT, &output_h, sizeof(output_h)));

tivxCheckStatus(&status, vxQueryImage(output, (vx_enum)VX_IMAGE_FORMAT, &output_fmt, sizeof(output_fmt)));

}

/* PARAMETER CHECKING */

if ((vx_status)VX_SUCCESS == status)

{

if ((configuration_size != sizeof(tivx_display_m2m_params_t)) ||

(strncmp(configuration_name, "tivx_display_m2m_params_t", sizeof(configuration_name)) != 0))

{

status = (vx_status)VX_ERROR_INVALID_PARAMETERS;

VX_PRINT(VX_ZONE_ERROR, "'configuration' should be a user_data_object of type:\n tivx_display_m2m_params_t \n");

}

else

{

status = vxCopyUserDataObject(configuration, 0, sizeof(tivx_display_m2m_params_t), ¶ms, (vx_enum)VX_READ_ONLY, (vx_enum)VX_MEMORY_TYPE_HOST);

}

if ((vx_status)VX_SUCCESS == status)

{

if(1U != params.numPipe)

{

status = (vx_status)VX_ERROR_INVALID_PARAMETERS;

VX_PRINT(VX_ZONE_ERROR, "'configuration.numPipe' should be set to 1 as blending is not supported currently \n");

}

}

if( ((vx_df_image)VX_DF_IMAGE_RGB != input_fmt) &&

((vx_df_image)VX_DF_IMAGE_RGBX != input_fmt) &&

((vx_df_image)VX_DF_IMAGE_UYVY != input_fmt) &&

((vx_df_image)VX_DF_IMAGE_YUYV != input_fmt) &&

((vx_df_image)VX_DF_IMAGE_NV12 != input_fmt))

{

status = (vx_status)VX_ERROR_INVALID_PARAMETERS;

VX_PRINT(VX_ZONE_ERROR, "'input' should be an image of type:\n VX_DF_IMAGE_RGB or VX_DF_IMAGE_RGBX or VX_DF_IMAGE_UYVY or VX_DF_IMAGE_NV12 \n");

}

if( ((vx_df_image)VX_DF_IMAGE_RGB != output_fmt) &&

((vx_df_image)VX_DF_IMAGE_RGBX != output_fmt) &&

((vx_df_image)VX_DF_IMAGE_UYVY != output_fmt) &&

((vx_df_image)VX_DF_IMAGE_YUYV != output_fmt) &&

((vx_df_image)VX_DF_IMAGE_NV12 != output_fmt))

{

status = (vx_status)VX_ERROR_INVALID_PARAMETERS;

VX_PRINT(VX_ZONE_ERROR, "'output' should be an image of type:\n VX_DF_IMAGE_RGB or VX_DF_IMAGE_RGBX or VX_DF_IMAGE_UYVY or VX_DF_IMAGE_NV12 \n");

}

if (params.enable_deiniterleave)

{

if (input_fmt != output_fmt)

{

status = (vx_status)VX_ERROR_INVALID_PARAMETERS;

VX_PRINT(VX_ZONE_ERROR, "Input and output formats must be same for de-interleaving\n");

}

if (((input_w % output_w) != 0) ||

((input_h % output_h) != 0) ||

((input_w % output_w) != (input_h % output_h)))

{

status = (vx_status)VX_ERROR_INVALID_PARAMETERS;

VX_PRINT(VX_ZONE_ERROR, "Incorrect input/output size\n");

}

}

}

return status;

}

static vx_status VX_CALLBACK tivxAddKernelDisplayM2MInitialize(vx_node node,

const vx_reference parameters[ ],

vx_uint32 num_params)

{

vx_status status = (vx_status)VX_SUCCESS;

tivxKernelValidRectParams prms;

if ( (num_params != TIVX_KERNEL_DISPLAY_M2M_MAX_PARAMS)

|| (NULL == parameters[TIVX_KERNEL_DISPLAY_M2M_CONFIGURATION_IDX])

|| (NULL == parameters[TIVX_KERNEL_DISPLAY_M2M_INPUT_IDX])

|| (NULL == parameters[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX])

)

{

status = (vx_status)VX_ERROR_INVALID_PARAMETERS;

VX_PRINT(VX_ZONE_ERROR, "One or more REQUIRED parameters are set to NULL\n");

}

if ((vx_status)VX_SUCCESS == status)

{

tivxKernelValidRectParams_init(&prms);

prms.in_img[0U] = (vx_image)parameters[TIVX_KERNEL_DISPLAY_M2M_INPUT_IDX];

prms.out_img[0U] = (vx_image)parameters[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX];

prms.num_input_images = 1;

prms.num_output_images = 1;

prms.top_pad = 0;

prms.bot_pad = 0;

prms.left_pad = 0;

prms.right_pad = 0;

prms.border_mode = VX_BORDER_UNDEFINED;

status = tivxKernelConfigValidRect(&prms);

}

return status;

}

vx_status tivxAddKernelDisplayM2M(vx_context context)

{

vx_kernel kernel;

vx_status status;

uint32_t index;

vx_enum kernel_id;

status = vxAllocateUserKernelId(context, &kernel_id);

if(status != (vx_status)VX_SUCCESS)

{

VX_PRINT(VX_ZONE_ERROR, "Unable to allocate user kernel ID\n");

}

if (status == (vx_status)VX_SUCCESS)

{

kernel = vxAddUserKernel(

context,

TIVX_KERNEL_DISPLAY_M2M_NAME,

kernel_id,

NULL,

TIVX_KERNEL_DISPLAY_M2M_MAX_PARAMS,

tivxAddKernelDisplayM2MValidate,

tivxAddKernelDisplayM2MInitialize,

NULL);

status = vxGetStatus((vx_reference)kernel);

}

if (status == (vx_status)VX_SUCCESS)

{

index = 0;

{

status = vxAddParameterToKernel(kernel,

index,

(vx_enum)VX_INPUT,

(vx_enum)VX_TYPE_USER_DATA_OBJECT,

(vx_enum)VX_PARAMETER_STATE_REQUIRED

);

index++;

}

if (status == (vx_status)VX_SUCCESS)

{

status = vxAddParameterToKernel(kernel,

index,

(vx_enum)VX_INPUT,

(vx_enum)VX_TYPE_IMAGE,

(vx_enum)VX_PARAMETER_STATE_REQUIRED

);

index++;

}

if (status == (vx_status)VX_SUCCESS)

{

status = vxAddParameterToKernel(kernel,

index,

(vx_enum)VX_OUTPUT,

(vx_enum)VX_TYPE_IMAGE,

(vx_enum)VX_PARAMETER_STATE_REQUIRED

);

index++;

}

if (status == (vx_status)VX_SUCCESS)

{

/* add supported target's */

tivxAddKernelTarget(kernel, TIVX_TARGET_DISPLAY_M2M1);

tivxAddKernelTarget(kernel, TIVX_TARGET_DISPLAY_M2M2);

tivxAddKernelTarget(kernel, TIVX_TARGET_DISPLAY_M2M3);

tivxAddKernelTarget(kernel, TIVX_TARGET_DISPLAY_M2M4);

}

if (status == (vx_status)VX_SUCCESS)

{

status = vxFinalizeKernel(kernel);

}

if (status != (vx_status)VX_SUCCESS)

{

vxReleaseKernel(&kernel);

kernel = NULL;

}

}

else

{

kernel = NULL;

}

vx_display_m2m_kernel = kernel;

return status;

}

vx_status tivxRemoveKernelDisplayM2M(vx_context context)

{

vx_status status;

vx_kernel kernel = vx_display_m2m_kernel;

status = vxRemoveKernel(kernel);

vx_display_m2m_kernel = NULL;

return status;

}

void tivx_display_m2m_params_init(tivx_display_m2m_params_t *prms)

{

uint32_t loopCnt;

prms->instId = 0U;

prms->numPipe = 1U;

for (loopCnt = 0U ; loopCnt < TIVX_DISPLAY_M2M_MAX_PIPE ; loopCnt++)

{

prms->pipeId[loopCnt] = 1U;

}

prms->overlayId = 0U;

prms->enable_deiniterleave = 1u;

}

/*

*

* Copyright (c) 2021 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

#include <stdio.h>

#include "TI/tivx.h"

#include "VX/vx.h"

#include "TI/tivx_event.h"

#include "tivx_hwa_kernels.h"

#include "tivx_kernel_display_m2m.h"

#include "TI/tivx_target_kernel.h"

#include "tivx_kernels_target_utils.h"

#include "tivx_hwa_display_m2m_priv.h"

#include <TI/tivx_queue.h>

#include <ti/drv/fvid2/fvid2.h>

#include <ti/drv/dss/dss.h>

#include <tivx_obj_desc_priv.h>

#include <vx_reference.h>

#define DISPLAY_MAX_VALID_PLANES 2U

#define DISPLAY_M2M_MAX_HANDLES (10)

typedef struct

{

/*! IDs=> 0: Write-back pipe-line1 */

uint32_t instId;

/*! Number of pipe-lines used, should be set to '1' as blending is not supported currently */

uint32_t numPipe;

/*! IDs=> 0:VID1, 1:VIDL1, 2:VID2 and 3:VIDL2 */

uint32_t pipeId[TIVX_DISPLAY_M2M_MAX_PIPE];

/*! IDs=> 0:Overlay1, 1:Overlay2, 2:Overlay3 and 3:Overlay4 */

uint32_t overlayId;

/*! FVID2 display driver handle */

Fvid2_Handle drvHandle;

/*! WB pipe create parameters */

Dss_WbCreateParams createParams;

/*! WB pipe create status */

Dss_WbCreateStatus createStatus;

/*! Callback parameters */

Fvid2_CbParams cbParams;

/*! WB pipe status */

Dss_WbStatus wbStatus;

/*! WB pipe configuration */

Dss_WbPipeCfgParams wbCfg;

/*! WB pipe DMA configuration */

CSL_DssWbPipeDmaCfg wbDmaCfg;

/*! WB pipe MFlag configuration */

Dss_WbPipeMflagParams wbMflagCfg;

/*! WB pipe CSC configuration */

CSL_DssCscCoeff wbCscCfg;

/*! Display pipe configuration */

Dss_PipeCfgParams pipeCfg[TIVX_DISPLAY_M2M_MAX_PIPE];

/*! Display pipe MFlag configuration */

Dss_PipeMflagParams mFlagCfg[TIVX_DISPLAY_M2M_MAX_PIPE];

/*! Display pipe CSC configuration */

Dss_PipeCscParams cscCfg[TIVX_DISPLAY_M2M_MAX_PIPE];

/*! Display Overlay configuration */

Dss_DctrlOverlayParams ovrCfg;

/*! Display Layer configuration */

Dss_DctrlOverlayLayerParams layerCfg;

/*! Display Global configuration */

Dss_DctrlGlobalDssParams globalParams;

/*! Mutex used for waiting for process completion */

tivx_event waitForProcessCmpl;

/*! Display M2M Driver Input Frame List, used for providing

* an array of input frames */

Fvid2_FrameList inFrmList;

/*! Display M2M Driver Output Frame List, used for providing

* an array of output frames */

Fvid2_FrameList outFrmList;

/*! Display M2M Driver Input Frames */

Fvid2_Frame inFrm[TIVX_DISPLAY_M2M_MAX_PIPE];

/*! Display M2M Driver Output Frames */

Fvid2_Frame outFrm[1U];

} tivxDisplayM2MDrvObj;

typedef struct

{

/*! IDs=> 0: Object free, 1: allocated */

uint32_t isAlloc;

/*! Display M2M driver object */

tivxDisplayM2MDrvObj drvObj;

/*! Display M2M Node create parameters provided by application */

tivx_display_m2m_params_t createParams;

uint32_t numOutImgs;

} tivxDisplayM2MParams;

typedef struct

{

tivx_mutex lock;

tivxDisplayM2MParams m2mObj[DISPLAY_M2M_MAX_HANDLES];

} tivxDisplayM2MInstObj;

static tivx_target_kernel vx_display_m2m_target_kernel1 = NULL;

static tivx_target_kernel vx_display_m2m_target_kernel2 = NULL;

static tivx_target_kernel vx_display_m2m_target_kernel3 = NULL;

static tivx_target_kernel vx_display_m2m_target_kernel4 = NULL;

tivxDisplayM2MInstObj gTivxDispM2mInstObj;

static vx_status VX_CALLBACK tivxDisplayM2MProcess(

tivx_target_kernel_instance kernel,

tivx_obj_desc_t *obj_desc[],

uint16_t num_params, void *priv_arg);

static vx_status VX_CALLBACK tivxDisplayM2MCreate(

tivx_target_kernel_instance kernel,

tivx_obj_desc_t *obj_desc[],

uint16_t num_params, void *priv_arg);

static vx_status VX_CALLBACK tivxDisplayM2MDelete(

tivx_target_kernel_instance kernel,

tivx_obj_desc_t *obj_desc[],

uint16_t num_params, void *priv_arg);

static vx_status VX_CALLBACK tivxDisplayM2MControl(

tivx_target_kernel_instance kernel,

uint32_t node_cmd_id, tivx_obj_desc_t *obj_desc[],

uint16_t num_params, void *priv_arg);

static vx_status tivxDisplayM2MSetCreateParams(

tivxDisplayM2MParams *prms,

const tivx_obj_desc_user_data_object_t *obj_desc,

const tivx_obj_desc_image_t *obj_desc_imageIn,

const tivx_obj_desc_image_t *obj_desc_imageOut);

static vx_status tivxDisplayM2MDrvStructsInit(tivxDisplayM2MDrvObj *drvObj);

static vx_status tivxDisplayM2MDrvCfg(tivxDisplayM2MDrvObj *drvObj);

static int32_t tivxDisplayM2MCallback(Fvid2_Handle handle, void *appData);

static vx_status tivxDisplayExtractFvid2Format(

const tivx_obj_desc_image_t *obj_desc_img,

Fvid2_Format *format);

static tivxDisplayM2MParams *tivxDispM2mAllocObject(tivxDisplayM2MInstObj *instObj);

static void tivxDispM2mFreeObject(tivxDisplayM2MInstObj *instObj,

tivxDisplayM2MParams *m2mObj);

static vx_status VX_CALLBACK tivxDisplayM2MProcess(

tivx_target_kernel_instance kernel,

tivx_obj_desc_t *obj_desc[],

uint16_t num_params, void *priv_arg)

{

vx_status status = (vx_status)VX_SUCCESS;

tivxDisplayM2MParams *prms = NULL;

tivxDisplayM2MDrvObj *drvObj;

tivx_obj_desc_image_t *input_desc;

tivx_obj_desc_image_t *output_desc;

void *input_target_ptr, *input_target_ptr2 = NULL;

void *output_target_ptr, *output_target_ptr2 = NULL;

Fvid2_Frame *frm;

int32_t fvid2_status = FVID2_SOK;

uint32_t pipeIdx, iterCnt;

if ( (num_params != TIVX_KERNEL_DISPLAY_M2M_MAX_PARAMS)

|| (NULL == obj_desc[TIVX_KERNEL_DISPLAY_M2M_CONFIGURATION_IDX])

|| (NULL == obj_desc[TIVX_KERNEL_DISPLAY_M2M_INPUT_IDX])

|| (NULL == obj_desc[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX])

)

{

status = (vx_status)VX_FAILURE;

}

if((vx_status)VX_SUCCESS == status)

{

uint32_t size;

input_desc = (tivx_obj_desc_image_t *)obj_desc[TIVX_KERNEL_DISPLAY_M2M_INPUT_IDX];

output_desc = (tivx_obj_desc_image_t *)obj_desc[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX];

status = tivxGetTargetKernelInstanceContext(kernel,

(void **)&prms, &size);

if (((vx_status)VX_SUCCESS != status) || (NULL == prms) ||

(sizeof(tivxDisplayM2MParams) != size))

{

status = (vx_status)VX_FAILURE;

VX_PRINT(VX_ZONE_ERROR, "DISPLAY M2M: ERROR: Instance context is NULL!\r\n");

}

}

if((vx_status)VX_SUCCESS == status)

{

/* Update 'input_desc' to array from only single image input to

support blending i.e. more than 1 number of pipes. */

input_target_ptr = tivxMemShared2TargetPtr(&input_desc->mem_ptr[0]);

VX_PRINT(VX_ZONE_INFO, "input_target_ptr = %p\n", input_target_ptr);

if((vx_df_image)VX_DF_IMAGE_NV12 == input_desc->format)

{

input_target_ptr2 = tivxMemShared2TargetPtr(&input_desc->mem_ptr[1]);

VX_PRINT(VX_ZONE_INFO, "input_target_ptr2 = %p\n", input_target_ptr2);

}

for (iterCnt = 0u; iterCnt < prms->numOutImgs; iterCnt ++)

{

output_desc = (tivx_obj_desc_image_t *)

tivxGetObjDescElement(obj_desc[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX],iterCnt);

output_target_ptr = tivxMemShared2TargetPtr(&output_desc->mem_ptr[0]);

VX_PRINT(VX_ZONE_INFO, "output_target_ptr = %p\n", output_target_ptr);

if((vx_df_image)VX_DF_IMAGE_NV12 == output_desc->format)

{

output_target_ptr2 = tivxMemShared2TargetPtr(&output_desc->mem_ptr[1]);

VX_PRINT(VX_ZONE_INFO, "output_target_ptr2 = %p\n", output_target_ptr2);

}

/* call kernel processing function */

drvObj = &prms->drvObj;

/* Assign input buffer addresses */

for (pipeIdx = 0U ; pipeIdx < drvObj->numPipe ; pipeIdx++)

{

frm = &drvObj->inFrm[pipeIdx];

frm->addr[0U] = ((uint64_t)input_target_ptr) +

iterCnt*input_desc->imagepatch_addr[0].stride_y;

if((vx_df_image)VX_DF_IMAGE_NV12 == input_desc->format)

{

frm->addr[1U] = ((uint64_t)input_target_ptr2) +

iterCnt*input_desc->imagepatch_addr[1].stride_y;

}

}

/* Assign output buffer addresses */

frm = drvObj->outFrm;

frm->addr[0U] = (uint64_t)output_target_ptr;

if((vx_df_image)VX_DF_IMAGE_NV12 == output_desc->format)

{

frm->addr[1U] = (uint64_t)output_target_ptr2;

}

/* Submit the request to the driver */

fvid2_status = Fvid2_processRequest(drvObj->drvHandle,

&drvObj->inFrmList,

&drvObj->outFrmList,

FVID2_TIMEOUT_FOREVER);

if (FVID2_SOK != fvid2_status)

{

VX_PRINT(VX_ZONE_ERROR, "Failed to Submit Request\n");

status = (vx_status)VX_FAILURE;

}

else

{

/* Wait for Frame Completion */

tivxEventWait(drvObj->waitForProcessCmpl, TIVX_EVENT_TIMEOUT_WAIT_FOREVER);

fvid2_status = Fvid2_getProcessedRequest(drvObj->drvHandle,

&drvObj->inFrmList,

&drvObj->outFrmList,

0);

if (FVID2_SOK != fvid2_status)

{

VX_PRINT(VX_ZONE_ERROR, "Failed to Get Processed Request\n");

status = (vx_status)VX_FAILURE;

}

}

}

/* kernel processing function complete */

}

return status;

}

static vx_status VX_CALLBACK tivxDisplayM2MCreate(

tivx_target_kernel_instance kernel,

tivx_obj_desc_t *obj_desc[],

uint16_t num_params, void *priv_arg)

{

vx_status status = (vx_status)VX_SUCCESS;

tivxDisplayM2MParams *prms = NULL;

tivx_obj_desc_user_data_object_t *configuration_desc;

tivx_obj_desc_image_t *obj_desc_imageIn, *obj_desc_imageOut;

if ( (num_params != TIVX_KERNEL_DISPLAY_M2M_MAX_PARAMS)

|| (NULL == obj_desc[TIVX_KERNEL_DISPLAY_M2M_CONFIGURATION_IDX])

|| (NULL == obj_desc[TIVX_KERNEL_DISPLAY_M2M_INPUT_IDX])

|| (NULL == obj_desc[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX])

)

{

status = (vx_status)VX_FAILURE;

}

else

{

configuration_desc = (tivx_obj_desc_user_data_object_t *)obj_desc[TIVX_KERNEL_DISPLAY_M2M_CONFIGURATION_IDX];

obj_desc_imageIn = (tivx_obj_desc_image_t *)obj_desc[TIVX_KERNEL_DISPLAY_M2M_INPUT_IDX];

obj_desc_imageOut = (tivx_obj_desc_image_t *)obj_desc[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX];

if (configuration_desc->mem_size != sizeof(tivx_display_m2m_params_t))

{

VX_PRINT(VX_ZONE_ERROR, "User data object size on target does not match the size on host, possibly due to misalignment in data structure\n");

status = (vx_status)VX_FAILURE;

}

prms = tivxDispM2mAllocObject(&gTivxDispM2mInstObj);

if (NULL == prms)

{

status = (vx_status)VX_ERROR_NO_MEMORY;

VX_PRINT(VX_ZONE_ERROR, "Unable to allocate local memory\n");

}

/* Create Node object elements */

if ((vx_status)VX_SUCCESS == status)

{

status = tivxDisplayM2MSetCreateParams(prms,

configuration_desc,

obj_desc_imageIn,

obj_desc_imageOut);

}

/* Create sync events */

if (status == (vx_status)VX_SUCCESS)

{

status = tivxEventCreate(&prms->drvObj.waitForProcessCmpl);

if ((vx_status)VX_SUCCESS != status)

{

VX_PRINT(VX_ZONE_ERROR, "Failed to allocate Event\n");

}

}

/* DSS M2M Driver create and configuration */

if (status == (vx_status)VX_SUCCESS)

{

status = tivxDisplayM2MDrvCfg(&prms->drvObj);

}

if ((vx_status)VX_SUCCESS == status)

{

tivxSetTargetKernelInstanceContext(kernel, prms, sizeof(tivxDisplayM2MParams));

}

else

{

status = (vx_status)VX_ERROR_NO_MEMORY;

VX_PRINT(VX_ZONE_ERROR, "Unable to allocate local memory\n");

}

}

return status;

}

static vx_status VX_CALLBACK tivxDisplayM2MDelete(

tivx_target_kernel_instance kernel,

tivx_obj_desc_t *obj_desc[],

uint16_t num_params, void *priv_arg)

{

vx_status status = (vx_status)VX_SUCCESS;

tivxDisplayM2MParams *prms = NULL;

uint32_t size;

int32_t fvid2_status = FVID2_SOK;

if ( (num_params != TIVX_KERNEL_DISPLAY_M2M_MAX_PARAMS)

|| (NULL == obj_desc[TIVX_KERNEL_DISPLAY_M2M_CONFIGURATION_IDX])

|| (NULL == obj_desc[TIVX_KERNEL_DISPLAY_M2M_INPUT_IDX])

|| (NULL == obj_desc[TIVX_KERNEL_DISPLAY_M2M_OUTPUT_IDX])

)

{

status = (vx_status)VX_FAILURE;

}

else

{

status = tivxGetTargetKernelInstanceContext(kernel,

(void **)&prms,

&size);

if ((vx_status)VX_SUCCESS != status)

{

VX_PRINT(VX_ZONE_ERROR, " DSS M2M: ERROR: Could not obtain kernel instance context !!!\n");

}

if(NULL == prms)

{

VX_PRINT(VX_ZONE_ERROR, "Kernel instance context is NULL!!!\n");

status = (vx_status)VX_FAILURE;

}

if ((vx_status)VX_SUCCESS == status)

{

/* Stop Display M2M Driver */

fvid2_status = Fvid2_stop(prms->drvObj.drvHandle, NULL);

if (FVID2_SOK != fvid2_status)

{

status = (vx_status)VX_FAILURE;

VX_PRINT(VX_ZONE_ERROR, " DSS M2M: ERROR: FVID2 DSS M2M not stopped !!!\n");

}

}

if ((vx_status)VX_SUCCESS == status)

{

/* Dequeue all the request from the driver */

while ((vx_status)VX_SUCCESS == status)

{

fvid2_status = Fvid2_getProcessedRequest(prms->drvObj.drvHandle,

&prms->drvObj.inFrmList,

&prms->drvObj.outFrmList,

0);

if (FVID2_SOK != fvid2_status)

{

if (fvid2_status != FVID2_ENO_MORE_BUFFERS)

{

VX_PRINT(VX_ZONE_ERROR, "Failed to Get Processed Request\n");

}

status = (vx_status)VX_FAILURE;

}

}

if (fvid2_status == FVID2_ENO_MORE_BUFFERS)

{

status = (vx_status)VX_SUCCESS;

}

}

if ((vx_status)VX_SUCCESS == status)

{

/* print status */

fvid2_status = Fvid2_control(prms->drvObj.drvHandle,

IOCTL_DSS_M2M_GET_CURRENT_STATUS,

&prms->drvObj.wbStatus,

NULL);

if (FVID2_SOK != fvid2_status)

{

VX_PRINT(VX_ZONE_ERROR, "Get status returned failure\n");

status = (vx_status)VX_FAILURE;

}

else

{

printf( "==========================================================\r\n");

printf( " Display M2M Status: Instance|%d\r\n", prms->drvObj.instId);

printf( "==========================================================\r\n");

printf( " Queue Count: %d\r\n", prms->drvObj.wbStatus.queueCount);

printf( " De-queue Count: %d\r\n", prms->drvObj.wbStatus.dequeueCount);

printf( " Write-back Frames Count: %d\r\n", prms->drvObj.wbStatus.wbFrmCount);

printf( " Underflow Count: %d\r\n", prms->drvObj.wbStatus.underflowCount);

}

}

if ((vx_status)VX_SUCCESS == status)

{

/* Delete FVID2 handle */

fvid2_status = Fvid2_delete(prms->drvObj.drvHandle, NULL);

if (FVID2_SOK != fvid2_status)

{

status = (vx_status)VX_FAILURE;

VX_PRINT(VX_ZONE_ERROR, " DSS M2M: ERROR: FVID2 Delete Failed !!!\n");

}

else

{

prms->drvObj.drvHandle = NULL;

}

}

if ((vx_status)VX_SUCCESS == status)

{

/* Delete event */

tivxEventDelete(&prms->drvObj.waitForProcessCmpl);

}

if ((NULL != prms) &&

(sizeof(tivxDisplayM2MParams) == size))

{

tivxDispM2mFreeObject(&gTivxDispM2mInstObj, prms);

//tivxMemFree(prms, size, (vx_enum)TIVX_MEM_EXTERNAL);

}

}

return status;

}

static vx_status VX_CALLBACK tivxDisplayM2MControl(

tivx_target_kernel_instance kernel,

uint32_t node_cmd_id, tivx_obj_desc_t *obj_desc[],

uint16_t num_params, void *priv_arg)

{

vx_status status = (vx_status)VX_SUCCESS;

int32_t fvid2_status = FVID2_SOK;

uint32_t size;

tivxDisplayM2MParams *prms = NULL;

tivxDisplayM2MDrvObj *drvObj;

tivx_display_m2m_statistics_t *m2m_status_prms = NULL;

void *target_ptr;

tivx_obj_desc_user_data_object_t *usr_data_obj;

status = tivxGetTargetKernelInstanceContext(kernel, (void **)&prms, &size);

if (((vx_status)VX_SUCCESS != status) ||

(NULL == prms) ||

(sizeof(tivxDisplayM2MParams) != size))

{

status = (vx_status)VX_FAILURE;

}

if (status == (vx_status)VX_SUCCESS)

{

switch (node_cmd_id)

{

case TIVX_DISPLAY_M2M_GET_STATISTICS:

{

if (NULL != obj_desc[0])

{

drvObj = &prms->drvObj;

fvid2_status = Fvid2_control(drvObj->drvHandle,

IOCTL_DSS_M2M_GET_CURRENT_STATUS,

&drvObj->wbStatus,

NULL);

if (FVID2_SOK != fvid2_status)

{

VX_PRINT(VX_ZONE_ERROR, "Get status returned failure\n");

status = (vx_status)VX_FAILURE;

}

else

{

/* Update return status object */

usr_data_obj = (tivx_obj_desc_user_data_object_t *)obj_desc[0U];

target_ptr = tivxMemShared2TargetPtr(&usr_data_obj->mem_ptr);

tivxCheckStatus(&status,

tivxMemBufferMap(target_ptr,

usr_data_obj->mem_size,

(vx_enum)VX_MEMORY_TYPE_HOST,

(vx_enum)VX_WRITE_ONLY));

if (sizeof(tivx_display_m2m_statistics_t) ==

usr_data_obj->mem_size)

{

m2m_status_prms = (tivx_display_m2m_statistics_t *)target_ptr;

m2m_status_prms->queueCount =

drvObj->wbStatus.queueCount;

m2m_status_prms->dequeueCount =

drvObj->wbStatus.dequeueCount;

m2m_status_prms->wbFrmCount =

drvObj->wbStatus.wbFrmCount;

m2m_status_prms->underflowCount =

drvObj->wbStatus.underflowCount;

}

else

{

VX_PRINT(VX_ZONE_ERROR, "Invalid Size \n");

status = (vx_status)VX_ERROR_INVALID_PARAMETERS;

}

tivxCheckStatus(&status,

tivxMemBufferUnmap(target_ptr,

usr_data_obj->mem_size,

(vx_enum)VX_MEMORY_TYPE_HOST,

(vx_enum)VX_WRITE_ONLY));

}

}

else

{

VX_PRINT(VX_ZONE_ERROR, "User data object was NULL\n");

status = (vx_status)VX_FAILURE;

}

break;

}

default:

{

VX_PRINT(VX_ZONE_ERROR, "Invalid Command Id\n");

status = (vx_status)VX_FAILURE;

break;

}

}

}

return status;

}

void tivxAddTargetKernelDisplayM2M(void)

{

vx_status status = (vx_status)VX_FAILURE;

char target_name[TIVX_TARGET_MAX_NAME];

vx_enum self_cpu;

self_cpu = tivxGetSelfCpuId();

if ( self_cpu == (vx_enum)TIVX_CPU_ID_MCU2_0 )

{

strncpy(target_name, TIVX_TARGET_DISPLAY_M2M1, TIVX_TARGET_MAX_NAME);

vx_display_m2m_target_kernel1 = tivxAddTargetKernelByName(

TIVX_KERNEL_DISPLAY_M2M_NAME,

target_name,

tivxDisplayM2MProcess,

tivxDisplayM2MCreate,

tivxDisplayM2MDelete,

tivxDisplayM2MControl,

NULL);

strncpy(target_name, TIVX_TARGET_DISPLAY_M2M2, TIVX_TARGET_MAX_NAME);

vx_display_m2m_target_kernel2 = tivxAddTargetKernelByName(

TIVX_KERNEL_DISPLAY_M2M_NAME,

target_name,

tivxDisplayM2MProcess,

tivxDisplayM2MCreate,

tivxDisplayM2MDelete,

tivxDisplayM2MControl,

NULL);

strncpy(target_name, TIVX_TARGET_DISPLAY_M2M3, TIVX_TARGET_MAX_NAME);

vx_display_m2m_target_kernel3 = tivxAddTargetKernelByName(

TIVX_KERNEL_DISPLAY_M2M_NAME,

target_name,

tivxDisplayM2MProcess,

tivxDisplayM2MCreate,

tivxDisplayM2MDelete,

tivxDisplayM2MControl,

NULL);

strncpy(target_name, TIVX_TARGET_DISPLAY_M2M4, TIVX_TARGET_MAX_NAME);

vx_display_m2m_target_kernel4 = tivxAddTargetKernelByName(

TIVX_KERNEL_DISPLAY_M2M_NAME,

target_name,

tivxDisplayM2MProcess,

tivxDisplayM2MCreate,

tivxDisplayM2MDelete,

tivxDisplayM2MControl,

NULL);

status = tivxMutexCreate(&gTivxDispM2mInstObj.lock);

if ((vx_status)VX_SUCCESS != status)

{

VX_PRINT(VX_ZONE_ERROR, "Failed to create Mutex\n");

}

else

{

memset(&gTivxDispM2mInstObj.m2mObj, 0x0,

sizeof(tivxDisplayM2MParams) * DISPLAY_M2M_MAX_HANDLES);

}

}

}

void tivxRemoveTargetKernelDisplayM2M(void)

{

vx_status status = (vx_status)VX_SUCCESS;

status = tivxRemoveTargetKernel(vx_display_m2m_target_kernel1);

if (status == (vx_status)VX_SUCCESS)

{

vx_display_m2m_target_kernel1 = NULL;

}

status = tivxRemoveTargetKernel(vx_display_m2m_target_kernel2);

if (status == (vx_status)VX_SUCCESS)

{

vx_display_m2m_target_kernel2 = NULL;

}

status = tivxRemoveTargetKernel(vx_display_m2m_target_kernel3);

if (status == (vx_status)VX_SUCCESS)

{

vx_display_m2m_target_kernel3 = NULL;

}

status = tivxRemoveTargetKernel(vx_display_m2m_target_kernel4);

if (status == (vx_status)VX_SUCCESS)

{

vx_display_m2m_target_kernel4 = NULL;

}

if (NULL != gTivxDispM2mInstObj.lock)

{

tivxMutexDelete(&gTivxDispM2mInstObj.lock);

}

}

static vx_status tivxDisplayM2MSetCreateParams(

tivxDisplayM2MParams *prms,

const tivx_obj_desc_user_data_object_t *obj_desc,

const tivx_obj_desc_image_t *obj_desc_imageIn,

const tivx_obj_desc_image_t *obj_desc_imageOut)

{

vx_status status = (vx_status)VX_SUCCESS;

void *cfgPtr;

tivx_display_m2m_params_t *createParams;

tivxDisplayM2MDrvObj *drvObj;

uint32_t pipeIdx, layerIdx, pitchIdx;

Dss_DispParams *dispParams;

CSL_DssWbPipeCfg *wbPipeCfg;

Dss_DctrlOverlayParams *ovrParams;

Dss_DctrlOverlayLayerParams *layerParams;

Fvid2_Frame *frm;

cfgPtr = tivxMemShared2TargetPtr(&obj_desc->mem_ptr);

tivxCheckStatus(&status, tivxMemBufferMap(cfgPtr, obj_desc->mem_size,

(vx_enum)VX_MEMORY_TYPE_HOST, (vx_enum)VX_READ_ONLY));

if (status == (vx_status)VX_SUCCESS)

{

createParams = (tivx_display_m2m_params_t *)cfgPtr;

memcpy(&prms->createParams, createParams, sizeof(tivx_display_m2m_params_t));

drvObj = &prms->drvObj;

/* Set Driver object */

drvObj->instId = createParams->instId;

drvObj->numPipe = createParams->numPipe;

drvObj->overlayId = createParams->overlayId;

memcpy(&drvObj->pipeId[0U],

&createParams->pipeId[0U],

sizeof(createParams->pipeId));

if (createParams->enable_deiniterleave)

{

tivx_obj_desc_t *obj_desc = (tivx_obj_desc_t *)obj_desc_imageOut;

if((vx_enum)obj_desc->type==(vx_enum)TIVX_OBJ_DESC_OBJARRAY)

{

tivx_obj_desc_object_array_t *obj_desc_obj_array;

obj_desc_obj_array = (tivx_obj_desc_object_array_t *)obj_desc;

prms->numOutImgs = 4;//obj_desc_obj_array->num_items;

}

else

{

if ((vx_enum)TIVX_OBJ_DESC_INVALID != (vx_enum)obj_desc->scope_obj_desc_id)

{

tivx_obj_desc_object_array_t *parent_obj_desc = NULL;

tivxGetObjDescList(

&obj_desc->scope_obj_desc_id,

(tivx_obj_desc_t**)&parent_obj_desc, 1);

if (parent_obj_desc != NULL)

{

prms->numOutImgs = 4;//parent_obj_desc->num_items;

}

else

{

prms->numOutImgs = 4u;

}

}

else

{

prms->numOutImgs = 4u;

}

}

}

else

{

prms->numOutImgs = 4u;

}

}

/* Initialize driver object */

if (status == (vx_status)VX_SUCCESS)

{

status = tivxDisplayM2MDrvStructsInit(drvObj);

}

/* set driver object parameters */

if (status == (vx_status)VX_SUCCESS)

{

/* Callback parameters */

drvObj->cbParams.cbFxn = (Fvid2_CbFxn) (&tivxDisplayM2MCallback);

drvObj->cbParams.appData = drvObj;

drvObj->createParams.numPipe = drvObj->numPipe;

drvObj->createParams.overlayId = drvObj->overlayId;

/* Set Display pipeline parameters */

for (pipeIdx = 0U ; pipeIdx < drvObj->numPipe ; pipeIdx++)

{

dispParams = &drvObj->pipeCfg[pipeIdx].cfgParams;

drvObj->createParams.pipeId[pipeIdx] = drvObj->pipeId[pipeIdx];

drvObj->pipeCfg[pipeIdx].pipeId = drvObj->pipeId[pipeIdx];

drvObj->mFlagCfg[pipeIdx].pipeId = drvObj->pipeId[pipeIdx];

drvObj->cscCfg[pipeIdx].pipeId = drvObj->pipeId[pipeIdx];

dispParams->pipeCfg.pipeType = CSL_DSS_VID_PIPE_TYPE_VID;

dispParams->layerPos.startX = 0U;

dispParams->layerPos.startY = 0U;

dispParams->pipeCfg.scEnable = FALSE;

dispParams->alphaCfg.globalAlpha = 0xFFU;

dispParams->alphaCfg.preMultiplyAlpha = FALSE;

status = tivxDisplayExtractFvid2Format(

obj_desc_imageIn,

&dispParams->pipeCfg.inFmt);

if (status == (vx_status)VX_SUCCESS)

{

/* Set video pipe output frame dimensions same as input as

no scaling is done in video pipe-line */

dispParams->pipeCfg.outWidth = dispParams->pipeCfg.inFmt.width;

dispParams->pipeCfg.outHeight = dispParams->pipeCfg.inFmt.height;

if (createParams->enable_deiniterleave)

{

for (pitchIdx = 0; pitchIdx < 3; pitchIdx ++)

{

dispParams->pipeCfg.inFmt.pitch[pitchIdx] =

dispParams->pipeCfg.inFmt.pitch[pitchIdx] * prms->numOutImgs;

}

}

}

else

{

status = (vx_status)VX_FAILURE;

VX_PRINT(VX_ZONE_ERROR, "Invalid Input Image\n");

break;

}

}

/* Set Display WB pipeline parameters */

if (((vx_status)VX_SUCCESS == status) && (pipeIdx > 0))

{

wbPipeCfg = &drvObj->wbCfg.pipeCfg;

/* Set WB pipe input frame dimensions same as video pipe input/output frame,

no scaling is done in video pipe, it will be done in WB pipe-line */

wbPipeCfg->inFmt.width = dispParams->pipeCfg.outWidth;

wbPipeCfg->inFmt.height = dispParams->pipeCfg.outHeight;

wbPipeCfg->inPos.startX = 0U;

wbPipeCfg->inPos.startY = 0U;

status = tivxDisplayExtractFvid2Format(obj_desc_imageOut,

&wbPipeCfg->outFmt);

if (status != (vx_status)VX_SUCCESS)

{

VX_PRINT(VX_ZONE_ERROR, "Invalid Input Image\n");

status = (vx_status)VX_FAILURE;

}

else

{

if ((wbPipeCfg->inFmt.width != wbPipeCfg->outFmt.width) ||

(wbPipeCfg->inFmt.height != wbPipeCfg->outFmt.height))

{

wbPipeCfg->scEnable = TRUE;

}

}

}

/* Set Display WB pipeline parameters */

if ((vx_status)VX_SUCCESS == status)

{

ovrParams = &drvObj->ovrCfg;

ovrParams->overlayId = drvObj->overlayId;

ovrParams->colorbarEnable = FALSE;

ovrParams->overlayCfg.colorKeyEnable = FALSE;

ovrParams->overlayCfg.colorKeySel = CSL_DSS_OVERLAY_TRANS_COLOR_DEST;

ovrParams->overlayCfg.backGroundColor = 0xc8c800U;

layerParams = &drvObj->layerCfg;

layerParams->overlayId = drvObj->overlayId;

/* Set all layer to invalid first and then update only used ones */

for(layerIdx = 0U ; layerIdx < CSL_DSS_VID_PIPE_ID_MAX ; layerIdx++)

{

layerParams->pipeLayerNum[layerIdx] = CSL_DSS_OVERLAY_LAYER_INVALID;

}

/* Currently blending is not supported so only one layer is used.

This code needs to updated when blending is supported. */

layerParams->pipeLayerNum[drvObj->createParams.pipeId[0U]] =

CSL_DSS_OVERLAY_LAYER_NUM_0;

}

/* Update frame-lists */

if ((vx_status)VX_SUCCESS == status)

{

drvObj->inFrmList.numFrames = drvObj->numPipe;

for (pipeIdx = 0U ; pipeIdx < drvObj->numPipe ; pipeIdx++)

{

frm = (Fvid2_Frame *) &drvObj->inFrm[pipeIdx];

frm->chNum = drvObj->createParams.pipeId[pipeIdx];

drvObj->inFrmList.frames[pipeIdx] = frm;

}

frm = (Fvid2_Frame *) &drvObj->outFrm[0U];

drvObj->outFrmList.frames[0U] = frm;

drvObj->outFrmList.numFrames = 1U;

}

}

return status;

}

static vx_status tivxDisplayM2MDrvStructsInit(tivxDisplayM2MDrvObj *drvObj)

{

vx_status status = (vx_status)VX_SUCCESS;

uint32_t loopCnt;

/* Initialize driver create parameters */

Dss_m2mCreateParamsInit(&drvObj->createParams);

/* Initialize driver call-back parameters */

Fvid2CbParams_init(&drvObj->cbParams);

/* Initialize driver pipe configuration parameters */

for (loopCnt = 0U ; loopCnt < drvObj->numPipe ; loopCnt++)

{

Dss_dispParamsInit(&drvObj->pipeCfg[loopCnt].cfgParams);

Dss_dispPipeMflagParamsInit(&drvObj->mFlagCfg[loopCnt].mFlagCfg);

CSL_dssCscCoeffInit(&drvObj->cscCfg[loopCnt].csc);

}

/* Initialize WB pipeline parameters */

Dss_m2mPipeCfgParamsInit(&drvObj->wbCfg);

CSL_dssWbPipeDmaCfgInit(&drvObj->wbDmaCfg);

Dss_m2mMFlagParamsInit(&drvObj->wbMflagCfg);

CSL_dssCscCoeffInit(&drvObj->wbCscCfg);

Dss_m2mStatusInit(&drvObj->wbStatus);

/* Initialize Display overlay parameters */

Dss_dctrlOverlayParamsInit(&drvObj->ovrCfg);

Dss_dctrlOverlayLayerParamsInit(&drvObj->layerCfg);

/* Initialize Display global parameters */

Dss_dctrlGlobalDssParamsInit(&drvObj->globalParams);

/* Initialize input and output frame lists */

Fvid2FrameList_init(&drvObj->inFrmList);

Fvid2FrameList_init(&drvObj->outFrmList);

return status;

}

static vx_status tivxDisplayM2MDrvCfg(tivxDisplayM2MDrvObj *drvObj)

{

vx_status status = (vx_status)VX_SUCCESS;

uint32_t loopCnt;

int32_t fvid2_status = FVID2_SOK;

/* Display M2M Driver create */

drvObj->drvHandle = Fvid2_create(DSS_M2M_DRV_ID,

drvObj->instId,

&drvObj->createParams,

&drvObj->createStatus,

&drvObj->cbParams);

if((NULL == drvObj->drvHandle) ||

(drvObj->createStatus.retVal != FVID2_SOK))

{

VX_PRINT(VX_ZONE_ERROR, ": Display M2M Create Failed!!!\r\n");

status = (vx_status)VX_FAILURE;

}

/* Display M2M pipe configuration */

if ((vx_status)VX_SUCCESS == status)

{

for (loopCnt = 0U ; loopCnt < drvObj->numPipe ; loopCnt++)

{

fvid2_status += Fvid2_control(drvObj->drvHandle,

IOCTL_DSS_M2M_SET_PIPE_PARAMS,

&drvObj->pipeCfg[loopCnt],

NULL);

fvid2_status += Fvid2_control(drvObj->drvHandle,

IOCTL_DSS_M2M_SET_PIPE_MFLAG_PARAMS,

&drvObj->mFlagCfg[loopCnt],

NULL);

if (FVID2_SOK != fvid2_status)

{

VX_PRINT(VX_ZONE_ERROR, ": Display M2M DISP IOCTL Failed!!!\r\n");

status = (vx_status)VX_FAILURE;

break;

}

}

}

/* Display M2M overlay configuration */

if ((vx_status)VX_SUCCESS == status)

{

fvid2_status += Fvid2_control(drvObj->drvHandle,

IOCTL_DSS_DCTRL_SET_OVERLAY_PARAMS,

&drvObj->ovrCfg,

NULL);

fvid2_status += Fvid2_control(drvObj->drvHandle,

IOCTL_DSS_DCTRL_SET_LAYER_PARAMS,

&drvObj->layerCfg,

NULL);

if (FVID2_SOK != fvid2_status)

{

VX_PRINT(VX_ZONE_ERROR, ": Display M2M Overlay IOCTL Failed!!!\r\n");

status = (vx_status)VX_FAILURE;

}

}

/* Display M2M global configuration */

if ((vx_status)VX_SUCCESS == status)

{

fvid2_status += Fvid2_control(drvObj->drvHandle,

IOCTL_DSS_DCTRL_SET_GLOBAL_DSS_PARAMS,

&drvObj->globalParams,

NULL);

if (FVID2_SOK != fvid2_status)

{

VX_PRINT(VX_ZONE_ERROR, ": Display M2M Global IOCTL Failed!!!\r\n");

status = (vx_status)VX_FAILURE;

}

}

/* Display M2M write-back pipe configuration */

if ((vx_status)VX_SUCCESS == status)

{

fvid2_status += Fvid2_control(drvObj->drvHandle,

IOCTL_DSS_M2M_SET_WB_PIPE_PARAMS,

&drvObj->wbCfg,

NULL);

fvid2_status += Fvid2_control(drvObj->drvHandle,

IOCTL_DSS_M2M_SET_WB_PIPE_MFLAG_PARAMS,

&drvObj->wbMflagCfg,

NULL);

fvid2_status += Fvid2_control(drvObj->drvHandle,

IOCTL_DSS_M2M_SET_WB_PIPE_DMA_CFG,

&drvObj->wbDmaCfg,

NULL);

if (FVID2_SOK != fvid2_status)

{

VX_PRINT(VX_ZONE_ERROR, ": Display M2M WB IOCTL Failed!!!\r\n");

status = (vx_status)VX_FAILURE;

}

}

/* Start Display M2M Driver */

if ((vx_status)VX_SUCCESS == status)

{

fvid2_status = Fvid2_start(drvObj->drvHandle, NULL);

if (FVID2_SOK != fvid2_status)

{

VX_PRINT(VX_ZONE_ERROR, ": Display M2M Driver Start Failed!!!\r\n");

status = (vx_status)VX_FAILURE;

}

}

return status;

}

static int32_t tivxDisplayM2MCallback(Fvid2_Handle handle, void *appData)

{

tivxDisplayM2MDrvObj *drvObj = (tivxDisplayM2MDrvObj *)(appData);

if ((NULL != drvObj) && (drvObj->waitForProcessCmpl != NULL))

{

tivxEventPost(drvObj->waitForProcessCmpl);

}

return (vx_status)VX_SUCCESS;

}

static vx_status tivxDisplayExtractFvid2Format(

const tivx_obj_desc_image_t *obj_desc_img,

Fvid2_Format *format)

{

vx_status status = (vx_status)VX_SUCCESS;

Fvid2Format_init(format);

format->width = obj_desc_img->imagepatch_addr[0].dim_x;

format->height = obj_desc_img->imagepatch_addr[0].dim_y;

format->ccsFormat = FVID2_CCSF_BITS8_PACKED;

format->scanFormat = FVID2_SF_PROGRESSIVE;

switch (obj_desc_img->format)

{

case (vx_df_image)TIVX_DF_IMAGE_RGB565:

format->dataFormat = FVID2_DF_BGR16_565;

format->pitch[FVID2_RGB_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

break;

case (vx_df_image)VX_DF_IMAGE_RGB:

format->dataFormat = FVID2_DF_RGB24_888;

format->pitch[FVID2_RGB_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

break;

case (vx_df_image)VX_DF_IMAGE_RGBX:

format->dataFormat = FVID2_DF_RGBX24_8888;

format->pitch[FVID2_RGB_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

break;

case (vx_df_image)TIVX_DF_IMAGE_BGRX:

format->dataFormat = FVID2_DF_BGRX32_8888;

format->pitch[FVID2_RGB_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

break;

case (vx_df_image)VX_DF_IMAGE_UYVY:

format->dataFormat = FVID2_DF_YUV422I_UYVY;

format->pitch[FVID2_YUV_INT_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

break;

case (vx_df_image)VX_DF_IMAGE_YUYV:

format->dataFormat = FVID2_DF_YUV422I_YUYV;

format->pitch[FVID2_YUV_INT_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

break;

case (vx_df_image)VX_DF_IMAGE_NV12:

format->dataFormat = FVID2_DF_YUV420SP_UV;

format->pitch[FVID2_YUV_SP_Y_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

format->pitch[FVID2_YUV_SP_CBCR_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[1].stride_y;

break;

case (vx_df_image)VX_DF_IMAGE_U16:

format->ccsFormat = FVID2_CCSF_BITS12_UNPACKED16;

format->dataFormat = FVID2_DF_YUV420SP_UV;

format->pitch[FVID2_YUV_SP_Y_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

format->pitch[FVID2_YUV_SP_CBCR_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

break;

case (vx_df_image)VX_DF_IMAGE_U8:

format->ccsFormat = FVID2_CCSF_BITS8_PACKED;

format->dataFormat = FVID2_DF_YUV420SP_UV;

format->pitch[FVID2_YUV_SP_Y_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

format->pitch[FVID2_YUV_SP_CBCR_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

break;

default:

status = (vx_status)VX_FAILURE;

break;

}

return status;

}

static tivxDisplayM2MParams *tivxDispM2mAllocObject(tivxDisplayM2MInstObj *instObj)

{

uint32_t cnt;

tivxDisplayM2MParams *m2mObj = NULL;

/* Lock instance mutex */

tivxMutexLock(instObj->lock);

for (cnt = 0U; cnt < DISPLAY_M2M_MAX_HANDLES; cnt ++)

{

if (0U == instObj->m2mObj[cnt].isAlloc)

{

m2mObj = &instObj->m2mObj[cnt];

memset(m2mObj, 0x0, sizeof(tivxDisplayM2MParams));

instObj->m2mObj[cnt].isAlloc = 1U;

break;

}

}

/* Release instance mutex */

tivxMutexUnlock(instObj->lock);

return (m2mObj);

}

static void tivxDispM2mFreeObject(tivxDisplayM2MInstObj *instObj,

tivxDisplayM2MParams *m2mObj)

{

uint32_t cnt;

/* Lock instance mutex */

tivxMutexLock(instObj->lock);

for (cnt = 0U; cnt < DISPLAY_M2M_MAX_HANDLES; cnt ++)

{

if (m2mObj == &instObj->m2mObj[cnt])

{

m2mObj->isAlloc = 0U;

break;

}

}

/* Release instance mutex */

tivxMutexUnlock(instObj->lock);

}

/*

*

* Copyright (c) 2017 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

#include <stdio.h>

#include <stdlib.h>

#include <unistd.h>

#include <string.h>

#include <assert.h>

#include <stdint.h>

#include <TI/tivx.h>

#include <utils/app_init/include/app_init.h>

#include <utils/mem/include/app_mem.h>

#include <sys/time.h>

FILE *fp_src_img = NULL;

char file_name[20] = "file_name";

FILE *fp_dst_img[4] = {0};

uint32_t payload = 0;

void *virt_addr1 = NULL;

void *virt_addr2 = NULL;

uint64_t phys_addr1 = 0;

uint64_t phys_addr2 = 0;

uint8_t *src_buf = NULL, *dest_buf = NULL;

uint32_t width = 1280U;

uint32_t pitch = 4U*2*1280U;

uint32_t height = 1285U;

uint32_t size = 0;

uint8_t *image_test = NULL;

void timer_print_start(int task_id)

{

struct timeval tv1;

gettimeofday(&tv1, NULL);

printf("DSS_M2M: task id %d start_time %ld s %ld us\n", task_id, tv1.tv_sec, tv1.tv_usec);

}

void timer_print_stop(int task_id)

{

struct timeval tv1;

gettimeofday(&tv1, NULL);

printf("DSS_M2M: task id %d stop_time %ld s %ld us\n", task_id, tv1.tv_sec, tv1.tv_usec);

}

int main(int argc, char *argv[])

{

int status = 0;

width = 1280U;

pitch = 4U*2*1280U;

height = 1285U;

size = pitch*height;

status = appInit();

if(status==0)

{

//int app_multi_cam_main(int argc, char* argv[]);

//status = app_multi_cam_main(argc, argv);

{

extern void main_dss_m2m_test();

virt_addr1 = appMemAlloc(APP_MEM_HEAP_DDR, size, 0);

virt_addr2 = appMemAlloc(APP_MEM_HEAP_DDR, size, 0);

if (virt_addr1 == NULL || virt_addr2 == NULL)

{

printf("UDMA: MEM alloc fail !");

}

src_buf = (uint8_t*)virt_addr1;

dest_buf = (uint8_t*)virt_addr2;

fp_src_img = fopen("img_raw.yuv", "r");

fread(src_buf, width*pitch, 1, fp_src_img);

//system("sync");

sleep(2);

main_dss_m2m_test();

#if 0

timer_print_start(7);

for(int j = 0; j < 4; j++)

{

for(int i = 0; i < height; i++)

{

memcpy(&dest_buf[j*width*2U*height + i*width*2U], &src_buf[j*width*2U + i*pitch], width*2U);

}

}

timer_print_stop(7);

#endif

//system("sync");

sleep(2);

for(int i = 0; i < 4; i++)

{

sprintf(file_name, "img_raw_ch%d.yuv", i);

fp_dst_img[i] = fopen(file_name, "w");

fwrite(&dest_buf[i*width*height*2U], width*height*2U, 1, fp_dst_img[i]);

}

}

appDeInit();

}

return status;

}

/*

*

* Copyright (c) 2021 Texas Instruments Incorporated

*

* All rights reserved not granted herein.

*

* Limited License.

*

* Texas Instruments Incorporated grants a world-wide, royalty-free, non-exclusive

* license under copyrights and patents it now or hereafter owns or controls to make,

* have made, use, import, offer to sell and sell ("Utilize") this software subject to the

* terms herein. With respect to the foregoing patent license, such license is granted

* solely to the extent that any such patent is necessary to Utilize the software alone.

* The patent license shall not apply to any combinations which include this software,

* other than combinations with devices manufactured by or for TI ("TI Devices").

* No hardware patent is licensed hereunder.

*

* Redistributions must preserve existing copyright notices and reproduce this license

* (including the above copyright notice and the disclaimer and (if applicable) source

* code license limitations below) in the documentation and/or other materials provided

* with the distribution

*

* Redistribution and use in binary form, without modification, are permitted provided

* that the following conditions are met:

*

* * No reverse engineering, decompilation, or disassembly of this software is

* permitted with respect to any software provided in binary form.

*

* * any redistribution and use are licensed by TI for use only with TI Devices.

*

* * Nothing shall obligate TI to provide you with source code for the software

* licensed and provided to you in object code.

*

* If software source code is provided to you, modification and redistribution of the

* source code are permitted provided that the following conditions are met:

*

* * any redistribution and use of the source code, including any resulting derivative

* works, are licensed by TI for use only with TI Devices.

*

* * any redistribution and use of any object code compiled from the source code

* and any resulting derivative works, are licensed by TI for use only with TI Devices.

*

* Neither the name of Texas Instruments Incorporated nor the names of its suppliers

*

* may be used to endorse or promote products derived from this software without

* specific prior written permission.

*

* DISCLAIMER.

*

* THIS SOFTWARE IS PROVIDED BY TI AND TI'S LICENSORS "AS IS" AND ANY EXPRESS

* OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

* OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

* IN NO EVENT SHALL TI AND TI'S LICENSORS BE LIABLE FOR ANY DIRECT, INDIRECT,

* INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

* BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY

* OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE

* OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

* OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

#include <VX/vx.h>

#include <TI/tivx.h>

#include "test_engine/test.h"

#include <TI/tivx_config.h>

#include <string.h>

#include <TI/tivx_task.h>

#include <TI/tivx_event.h>

#include "math.h"

#include <limits.h>

#include <utils/mem/include/app_mem.h>

#include "test_tiovx/test_tiovx.h"

#include "test_hwa_common.h"

#define TIVX_TARGET_DEFAULT_STACK_SIZE (256U * 1024U)

#define TIVX_TARGET_DEFAULT_TASK_PRIORITY1 (8u)

#define DSS_M2M_NUM_CH (1U)

#define DSS_M2M_NUM_CH_MAX (4U)

/* Common Configurations across channels */

#define DSS_M2M_WB_PIPE_INST_ID (0U)

#define DSS_M2M_PIPE_NUM (1U)

#define DSS_M2M_PIPE_INST_ID (3U)

/* Currently Only Overlay2 can be used for M2M operations,

this can be changed through DSS initialization API available in vision_apps */

#define DSS_M2M_OVERLAY_ID (3U)

/* Channel 0 configurations */

#define DSS_M2M_CH0_IN_FRAME_FORMAT (VX_DF_IMAGE_UYVY)