Hi

Can you please provide examples of use of EDMA with ping pong and MCBSP with interrupt

the example you provided previously did not had MCBSP interrupt.

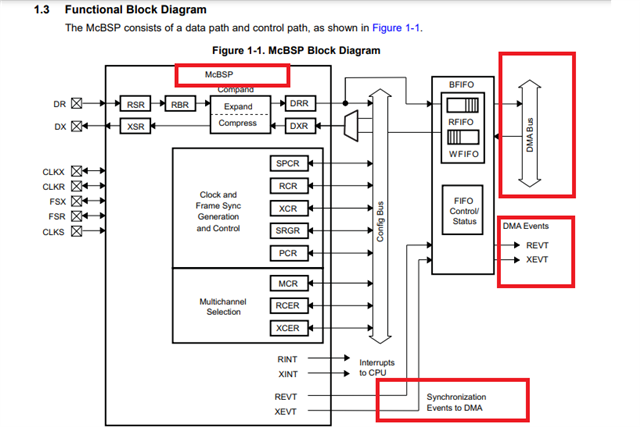

it should be noted the MCBSP interrupt event is located in Table 6-27 CIC0 events table

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.