Part Number: TDA4VM

Hello, I am configuring the features of QBV with the cpsw9g switch on TDA4VM, here is my test environment:

I want to configure the gating time to 1s on the CPSW9G switch and I get an error:\

Here are the commands I used to configure qbv:

|

#/bin/sh ifconfig eth2 down ifconfig eth4 down ifconfig eth1 down ifconfig eth3 down #设置队列数 ethtool -L eth2 tx 2 ethtool -L eth4 tx 2 ethtool -L eth1 tx 2 #禁用 eth0 网卡的 ptype-rrobin 接收队列策略 ethtool --set-priv-flags eth2 p0-rx-ptype-rrobin off ethtool --set-priv-flags eth4 p0-rx-ptype-rrobin off ethtool --set-priv-flags eth1 p0-rx-ptype-rrobin off ip link set dev eth1 up ip link set dev eth2 up ip link set dev eth3 up ip link set dev eth4 up sleep 10 #设置网桥 devlink dev param set platform/c000000.ethernet name switch_mode value true cmode runtime ip link add name br0 type bridge ip link set dev br0 type bridge ageing_time 1000 sleep 5 ip link set dev eth1 master br0 ip link set dev eth2 master br0 ip link set dev eth3 master br0 ip link set dev eth4 master br0 ifconfig br0 up bridge vlan add dev eth2 vid 30 master bridge vlan add dev eth4 vid 30 master ip link set dev br0 type bridge vlan_filtering 1 bridge vlan add dev br0 vid 1 pvid untagged self bridge vlan show #设置qbv base=0 tc qdisc replace dev eth2 parent root handle 100 taprio \ num_tc 2 \ map 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 \ queues 1@0 1@1 \ base-time $base \ sched-entry S 2 1000000000 \ sched-entry S 1 1000000000 \ flags 2 |

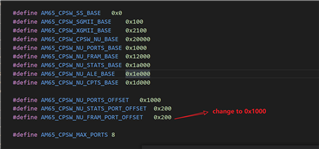

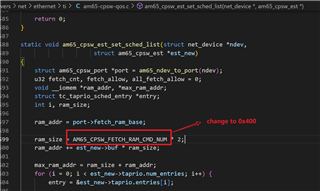

To fix this, I tried modifying the am65-cpsw-qos.c file:

#define AM65_CPSW_FETCH_RAM_CMD_NUM 0x80

Modified to:

#define AM65_CPSW_FETCH_RAM_CMD_NUM 0x8000

After the reconfiguration, there is no error, but I tested eth0.30 on J7200 and eth.30 on j7_vm, and found that the ping test failed, and the configuration qbv did not take effect.

1. Is it possible to set the gating time of QBV on TDA4VM to 1s?

2. If so, what changes need to be made?