Dear TI Engineering Team

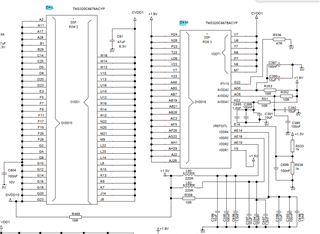

We are using a TMS320C6678 DSP in our design. We do not use the DDR memory and the signals are left open.

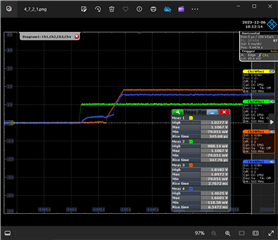

Voltage order is okay.

DDRCLKP is connected to +1.8V and DDRCLKN is connected to GND via a 1 kohm resistor.

DVDD15 is connected to +1.5V via a 10 ohm resistor.

We have noted that on some units DVDD15 starts at +1.5V and after 200ms it drops to +1V and after another 200ms it drops to +0.7V.

The other side of the 10ohm resistor stays at +1.5V.

Not all units behave like this. Do we have a flaw in our DSPs?

Or doesn't this voltage drop matters?

Best Regards

Lars-Olle Arnesson

Blue is DVDD15