Other Parts Discussed in Thread: J784S4XEVM, TDA4VH

Hi experts,

we test the lockstep mode of mcu domain of TDA4VH on J784S4XEVM.

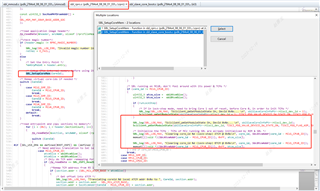

I am using SDK8.6,Below are my test steps:

1. Compile SBL. Enter ti-processor-sdk-rtos-j784s4-evm-08_06_01_03\pdk_j784s4_08_06_01_03\packages\ti\build directory.

make -j BOARD=j784s4_evm CORE=mcu1_0 BUILD_PROFILE=release sbl_mmcsd_img

2. Compile boot_app. Enter ti-processor-sdk-rtos-j784s4-evm-08_06_01_03\pdk_j784s4_08_06_01_03\packages\ti\build directory.

make BOARD=j784s4_evm CORE=mcu1_0 boot_app_mmcsd_linux -sj

3. Generating lockstep APP

multicoreImageGen LE 55 app 27 sbl_boot_app_mmcsd_linux_j784s4_evm_mcu1_0_freertos_TestApp_release.rprc

4. Starting with SBL using SD card

5. If the R core of the main domain is also set to lock step mode, it can start normally.

6. If the R core of the main domain is not configured in lockstep mode, the startup will jam.

Log as follows:

SBL Revision: 01.00.10.01 (Nov 24 2023 - 09:43:53)

TIFS ver: 8.6.3--1-g2249f (Chill Capybara

SCISERVER Board Configuration header population... PASSED

Sciclient_setBoardConfigHeader... PASSED

Initlialzing PLLs ...done.

InitlialzingClocks ...done.

Initlialzing DDR ...done.

Initializing GTC ...Begin parsing user application

Calling Sciclient_procBootRequestProcessor, ProcId 0x20...

Calling Sciclient_procBootRequestProcessor, ProcId 0x21...

Calling Sciclient_procBootRequestProcessor, ProcId 0x22...

Calling Sciclient_procBootRequestProcessor, ProcId 0x23...

Calling Sciclient_procBootRequestProcessor, ProcId 0x24...

Calling Sciclient_procBootRequestProcessor, ProcId 0x25...

Calling Sciclient_procBootRequestProcessor, ProcId 0x26...

Calling Sciclient_procBootRequestProcessor, ProcId 0x27...

Calling Sciclient_procBootRequestProcessor, ProcId 0x1...

Calling Sciclient_procBootRequestProcessor, ProcId 0x2...

Calling Sciclient_procBootRequestProcessor, ProcId 0x6...

Calling Sciclient_procBootRequestProcessor, ProcId 0x7...

Calling Sciclient_procBootRequestProcessor, ProcId 0x8...

Calling Sciclient_procBootRequestProcessor, ProcId 0x9...

Calling Sciclient_procBootRequestProcessor, ProcId 0xa...

Calling Sciclient_procBootRequestProcessor, ProcId 0xb...

Calling Sciclient_procBootRequestProcessor, ProcId 0x30...

Calling Sciclient_procBootRequestProcessor, ProcId 0x31...

Calling Sciclient_procBootRequestProcessor, ProcId 0x32...

Calling Sciclient_procBootRequestProcessor, ProcId 0x33...

Calling Sciclient_procBootRequestProcessor, ProcId 0x80...

Searching for X509 certificate ...not found

Switching core id 8, proc_id 0x1 to split mode...

Calling Sciclient_procBootGetProcessorState, ProcId 0x1...

Sciclient_procBootSetProcessorCfg, ProcId 0x1, enabling split mode...

Calling Sciclient_procBootGetProcessorState, ProcId 0x1...

Enabling MCU TCMs after reset for core 8

Disabling HW-based memory init of MCU TCMs for core 8

Sciclient_procBootSetProcessorCfg update TCM enable/disable settings...

Copying 0x40 bytes to 0x0

Copying 0x25dc0 bytes to 0x41c82000

Copying 0xc500 bytes to 0x41cb8980

Copying 0x4f88 bytes to 0x41ccce80

Copying 0x1604 bytes to 0x41cd1e80

Copying 0x460 bytes to 0x41cd3488

Copying 0x448 bytes to 0x41cd38e8

Copying 0x318 bytes to 0x41cd3d30

Copying 0x100 bytes to 0x41cd4048

Copying 0x27b8 bytes to 0x41cd4148

Setting entry point for core 8 @0x0

Sciclient_procBootReleaseProcessor, ProcId 0x20...

Sciclient_procBootReleaseProcessor, ProcId 0x21...

Sciclient_procBootReleaseProcessor, ProcId 0x22...

Sciclient_procBootReleaseProcessor, ProcId 0x23...

Sciclient_procBootReleaseProcessor, ProcId 0x24...

Sciclient_procBootReleaseProcessor, ProcId 0x25...

Sciclient_procBootReleaseProcessor, ProcId 0x26...

Sciclient_procBootReleaseProcessor, ProcId 0x27...

Sciclient_procBootReleaseProcessor, ProcId 0x1...

Sciclient_procBootReleaseProcessor, ProcId 0x2...

Sciclient_procBootReleaseProcessor, ProcId 0x6...

Sciclient_procBootReleaseProcessor, ProcId 0x7...

Sciclient_procBootReleaseProcessor, ProcId 0x8...

Sciclient_procBootReleaseProcessor, ProcId 0x9...

Sciclient_procBootReleaseProcessor, ProcId 0xa...

Sciclient_procBootReleaseProcessor, ProcId 0xb...

Sciclient_procBootReleaseProcessor, ProcId 0x30...

Sciclient_procBootReleaseProcessor, ProcId 0x31...

Sciclient_procBootReleaseProcessor, ProcId 0x32...

Sciclient_procBootReleaseProcessor, ProcId 0x33...

Sciclient_procBootReleaseProcessor, ProcId 0x80...

Calling Sciclient_procBootRequestProcessor, ProcId 0x1...

Sciclient_procBootSetProcessorCfg, ProcId 0x1, EntryPoint 0x0...

Sciclient_pmSetModuleClkFreq, DevId 0x15a @ 1000000000Hz...

Calling Sciclient_procBootRequestProcessor, ProcId 0x2...

Skipping Sciclient_procBootSetProcessorCfg for ProcId 0x2, EntryPoint 0xfffffffe...

Calling Sciclient_procBootRequestProcessor, ProcId 0x1...

Starting Sciserver..... PASSED

MCU R5F App started at 0 usecs

Loading BootImage

BootApp_MMCBootImageLate: fp 0x 0x41c12300, fileName is 0:/lateapp1

Searching for X509 certificate ...not found

Switching core id 10, proc_id 0x6 to split mode...

Calling Sciclient_procBootGetProcessorState, ProcId 0x6...

Sciclient_procBootSetProcessorCfg, ProcId 0x6, enabling split mode...

Sciclient_pmSetModuleState Off, DevId 0x153...

Calling Sciclient_procBootGetProcessorState, ProcId 0x6...

Enabling MCU TCMs after reset for core 10

Disabling HW-based memory init of MCU TCMs for core 10

Sciclient_procBootSetProcessorCfg update TCM enable/disable settings...

Setting HALT for ProcId 0x6...

Sciclient_pmSetModuleState On, DevId 0x153...

Clearing core_id 10 (lock-step) ATCM @ 0x5c00000