Hello Team,

We are using the RAT with the CLS_Rat...() functions in a Jacinto DRA829J based project from the R5FSS1_CORE0 core.

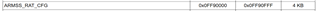

For specific use cases, we need to read the RAT registers.

Unfortunately, in the J721E TRM (spruil1c.pdf) we did not find the Base Address of the RAT Instances for the R5FSS, like it is normaly the case for the other processor modules. We've also searched in the register documents.

They are some RAT references in the TRM chapter 2.4 "Processors View Map", but they are only 4 regions defined for the MAIN_R5FSS cores (and 3 regions for the MCU_R5FSS cores), not 16 regions like explained in the TRM chapter 8.4.

- Are these regions addresses in the chapter 2.4 the RAT base addresses? If yes, where are the 12 other ones?

- If not, where are defined the RAT base adresses?

Many thanks in advance for your help.

Regards,

Vinod Alase