Other Parts Discussed in Thread: TDA4VH

Hi TI Experts,

Customer is working on TDA4VH SDK9.0.

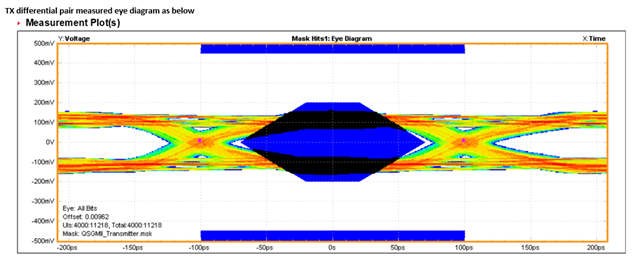

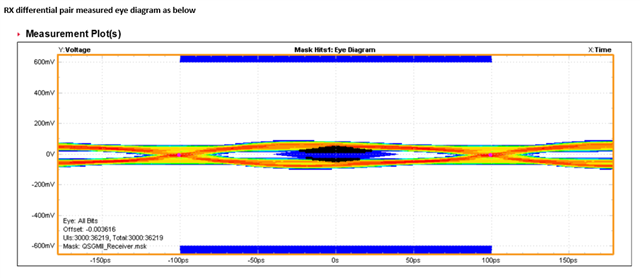

They have finished their customer board recently and started testing their QSGMII serdes eye diagram.

They have found the problem showing that the voltage amplitude could not meet the QSGMII Spec requirement shown below (blue part is the pattern per QSGMII spec).

Based on the above problem, customer may need know the following points, which may help debug this problem.

1: Is it feasible to increase the serdes driver side driving amplitude by serdes register configuration?

2: What would be the most possible reasons that lead to such issue like lack of signal amplitude?

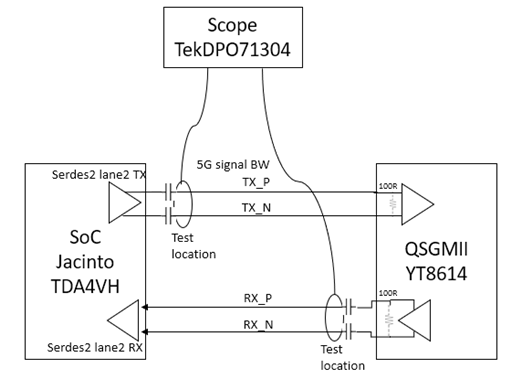

3: Do we have a layout guideline or recommendation for SGMII and QSGMII serdes interface and routing? We are confused for the high speed differential AC coupling cap location, it should be near output driver side (tx) or receiver side (rx)? It seems different documents have different arguments.

4: We do notice that the QSGMII PHY has a 100ohm resistor terminated between drive and receive differential pairs, does Jacinto serdes has 100ohm resistor terminated internally?

5: What is the differential signal type for serdes TX/RX differential pairs for TDA4VH? Is it LP-HCSL or CML or other type? We could not find it from the datasheet. In the datasheet it just mentions REF_CLK is HCSL.

6: Currently we use AC coupling cap (0.1uF X7S C0201 6.3V), do you have some suggestion here as we see the EVM board uses 0.22uF?

Thanks a lot!

Kevin