Other Parts Discussed in Thread: TDA4VH

Hi TI DDR Expert,

Customer is working on TDA4VH SDK9.0.

They have 2 generations of their customer board. For the first generation, they are using MT53E1G32D2FW-046 WT:C DDR type, and there is no problem.

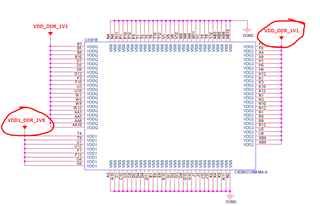

However, in their second generation boards, they are using CXDB5CCBM-MA-A DDR type, and having the below problem.

We have tried the following 6 debugging methods, and the corresponding results are provided below, pls have a look, thanks!

1: They have built 20 second generation boards, and only 1 board has this problem.

2: This is not about the soldering problem, because in the 30 time booting experiments only 3 times will have this problem. (the frequency of occurrence is about 10% for this problem board)

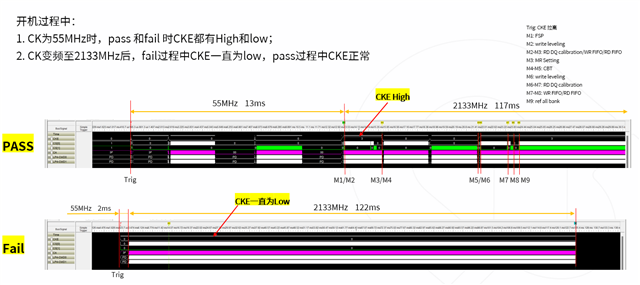

3: We have tried the experiment of decreasing the frequency, and got the below results.

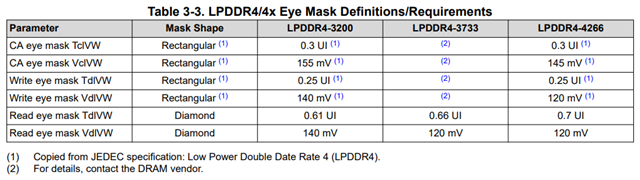

At the original frequency of 4266Mb/s, 3 times will fail out of 30 experiments, failure rate is 10%

Decrease frequency to 3733Mb/s, 30 times will all fail out of 30 experiments, failure rate is 100%

Decrease frequency to 3200Mb/s, 0 time will fail out of 30 experiments, failure rate is 0%

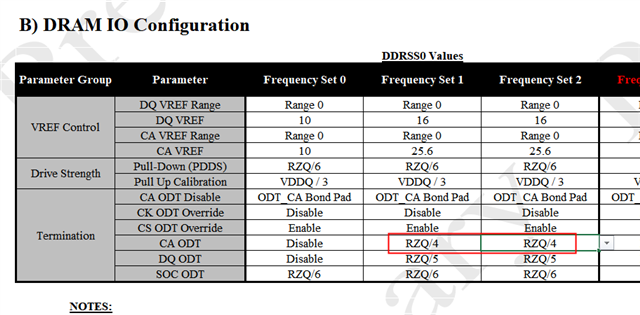

4: We have tried the experiment of changing the ODT pull down resistor of DQ/DQS, and got the below results (at the original frequency of 4266Mb/s).

Change the ODT pull down resistor of DQ/DQS to 60ohm, 1 time will fail out of 30 experiments, failure rate is 3%

Change the ODT pull down resistor of DQ/DQS to 80ohm, 4 time will fail out of 30 experiments, failure rate is 13%

5: We have tried increasing the VDD1 (default is 1.8V) & VDD2 (default is 1.1V) a little bit, and got the below results (at the original frequency of 4266Mb/s).

Change the VDD1 from 1.8V to 1.85V (increase 50mV), 5 time will fail out of 30 experiments, failure rate is 17%

Change the VDD1 from 1.8V to 1.85V (increase 50mV) and change the VDD2 from 1.1V to 1.11V (increase 10mV), 3 time will fail out of 30 experiments, failure rate is 10%

Change the VDD1 from 1.8V to 1.85V (increase 50mV) and change the VDD2 from 1.1V to 1.12V (increase 20mV), 2 time will fail out of 30 experiments, failure rate is 7%

Change the VDD1 from 1.8V to 1.85V (increase 50mV) and change the VDD2 from 1.1V to 1.13V (increase 30mV), 2 time will fail out of 30 experiments, failure rate is 7%

Change the VDD1 from 1.8V to 1.85V (increase 50mV) and change the VDD2 from 1.1V to 1.15V (increase 50mV), 0 time will fail out of 100+ experiments, failure rate is 0%

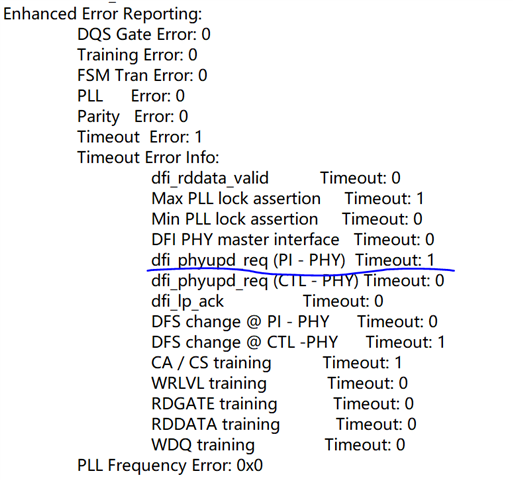

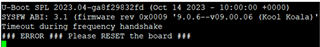

6: When the problem occurs, we have run the below suggested debugging tool. We load it to R5f core and run in the CCS, the corresponding log is attached below.

Error Training Log:

Console: [MCU_Cortex_R5_0] Training Results; Frequency 0; CS 0 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x23 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x25 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x26 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x23 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 30b CA Bit 1 delay: 318 CA Bit 2 delay: 31f CA Bit 3 delay: 31f CA Bit 4 delay: 317 CA Bit 5 delay: 33b Write Leveling: DQ Lane 0 WRDQS: 0xba DQ Lane 1 WRDQS: 0xec DQ Lane 2 WRDQS: 0xae DQ Lane 3 WRDQS: 0xba DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 508 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 424 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 436 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 400 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 120 read_delay_rise, dq0 : 144 read_delay_fall, dq1 : 120 read_delay_rise, dq1 : 144 read_delay_fall, dq2 : 126 read_delay_rise, dq2 : 150 read_delay_fall, dq3 : 126 read_delay_rise, dq3 : 150 read_delay_fall, dq4 : 120 read_delay_rise, dq4 : 144 read_delay_fall, dq5 : 120 read_delay_rise, dq5 : 150 read_delay_fall, dq6 : 120 read_delay_rise, dq6 : 138 read_delay_fall, dq7 : 126 read_delay_rise, dq7 : 144 read_delay_fall, dq8 : 132 read_delay_rise, dq8 : 144 read_delay_fall, dq9 : 132 read_delay_rise, dq9 : 150 read_delay_fall, dq10 : 126 read_delay_rise, dq10 : 144 read_delay_fall, dq11 : 120 read_delay_rise, dq11 : 150 read_delay_fall, dq12 : 126 read_delay_rise, dq12 : 144 read_delay_fall, dq13 : 132 read_delay_rise, dq13 : 150 read_delay_fall, dq14 : 126 read_delay_rise, dq14 : 138 read_delay_fall, dq15 : 138 read_delay_rise, dq15 : 150 read_delay_fall, dq16 : 138 read_delay_rise, dq16 : 144 read_delay_fall, dq17 : 150 read_delay_rise, dq17 : 150 read_delay_fall, dq18 : 132 read_delay_rise, dq18 : 132 read_delay_fall, dq19 : 150 read_delay_rise, dq19 : 150 read_delay_fall, dq20 : 132 read_delay_rise, dq20 : 132 read_delay_fall, dq21 : 138 read_delay_rise, dq21 : 138 read_delay_fall, dq22 : 132 read_delay_rise, dq22 : 132 read_delay_fall, dq23 : 126 read_delay_rise, dq23 : 132 read_delay_fall, dq24 : 120 read_delay_rise, dq24 : 114 read_delay_fall, dq25 : 126 read_delay_rise, dq25 : 138 read_delay_fall, dq26 : 132 read_delay_rise, dq26 : 114 read_delay_fall, dq27 : 126 read_delay_rise, dq27 : 126 read_delay_fall, dq28 : 126 read_delay_rise, dq28 : 114 read_delay_fall, dq29 : 132 read_delay_rise, dq29 : 132 read_delay_fall, dq30 : 138 read_delay_rise, dq30 : 126 read_delay_fall, dq31 : 126 read_delay_rise, dq31 : 120 Write DQ Training: write_delay, dq0 : 1157 write_delay, dq1 : 1157 write_delay, dq2 : 1146 write_delay, dq3 : 1146 write_delay, dq4 : 1146 write_delay, dq5 : 1146 write_delay, dq6 : 1146 write_delay, dq7 : 1146 write_delay, dq8 : 1125 write_delay, dq9 : 1125 write_delay, dq10 : 1136 write_delay, dq11 : 1136 write_delay, dq12 : 1136 write_delay, dq13 : 1136 write_delay, dq14 : 1136 write_delay, dq15 : 1136 write_delay, dq16 : 1144 write_delay, dq17 : 1133 write_delay, dq18 : 1154 write_delay, dq19 : 1133 write_delay, dq20 : 1133 write_delay, dq21 : 1133 write_delay, dq22 : 1133 write_delay, dq23 : 1144 write_delay, dq24 : 1163 write_delay, dq25 : 1141 write_delay, dq26 : 1163 write_delay, dq27 : 1163 write_delay, dq28 : 1163 write_delay, dq29 : 1141 write_delay, dq30 : 1152 write_delay, dq31 : 1163 Calibration Registers: CAL_OBS_0: 0x00814756 CAL_OBS_2: 0x00814813 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00147564 CAL_OBS_5: 0x00148138 CAL_OBS_6: 0x00f4756f CAL_OBS_7: 0x03f4813f CS Programmed Delays: phy_grp0_slave_delay_0: 0x033a phy_grp1_slave_delay_0: 0x033a phy_grp2_slave_delay_0: 0x0330 phy_grp3_slave_delay_0: 0x033a phy_grp0_slave_delay_1: 0x0330 phy_grp1_slave_delay_1: 0x033a phy_grp2_slave_delay_1: 0x0330 phy_grp3_slave_delay_1: 0x0330 phy_top_train_calib_error_info: 0x00000000 Training Results; Frequency 0; CS 1 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x23 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x25 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x26 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x23 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 30b CA Bit 1 delay: 318 CA Bit 2 delay: 31f CA Bit 3 delay: 31f CA Bit 4 delay: 317 CA Bit 5 delay: 33b Write Leveling: DQ Lane 0 WRDQS: 0xa2 DQ Lane 1 WRDQS: 0xde DQ Lane 2 WRDQS: 0xba DQ Lane 3 WRDQS: 0xba DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 460 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 376 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 436 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 400 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 132 read_delay_rise, dq0 : 144 read_delay_fall, dq1 : 120 read_delay_rise, dq1 : 144 read_delay_fall, dq2 : 132 read_delay_rise, dq2 : 156 read_delay_fall, dq3 : 132 read_delay_rise, dq3 : 156 read_delay_fall, dq4 : 126 read_delay_rise, dq4 : 144 read_delay_fall, dq5 : 126 read_delay_rise, dq5 : 150 read_delay_fall, dq6 : 120 read_delay_rise, dq6 : 144 read_delay_fall, dq7 : 126 read_delay_rise, dq7 : 150 read_delay_fall, dq8 : 132 read_delay_rise, dq8 : 150 read_delay_fall, dq9 : 132 read_delay_rise, dq9 : 156 read_delay_fall, dq10 : 132 read_delay_rise, dq10 : 144 read_delay_fall, dq11 : 132 read_delay_rise, dq11 : 150 read_delay_fall, dq12 : 126 read_delay_rise, dq12 : 144 read_delay_fall, dq13 : 138 read_delay_rise, dq13 : 150 read_delay_fall, dq14 : 126 read_delay_rise, dq14 : 144 read_delay_fall, dq15 : 144 read_delay_rise, dq15 : 150 read_delay_fall, dq16 : 120 read_delay_rise, dq16 : 138 read_delay_fall, dq17 : 150 read_delay_rise, dq17 : 156 read_delay_fall, dq18 : 132 read_delay_rise, dq18 : 144 read_delay_fall, dq19 : 150 read_delay_rise, dq19 : 144 read_delay_fall, dq20 : 132 read_delay_rise, dq20 : 138 read_delay_fall, dq21 : 138 read_delay_rise, dq21 : 138 read_delay_fall, dq22 : 138 read_delay_rise, dq22 : 150 read_delay_fall, dq23 : 132 read_delay_rise, dq23 : 144 read_delay_fall, dq24 : 114 read_delay_rise, dq24 : 120 read_delay_fall, dq25 : 126 read_delay_rise, dq25 : 132 read_delay_fall, dq26 : 126 read_delay_rise, dq26 : 126 read_delay_fall, dq27 : 126 read_delay_rise, dq27 : 138 read_delay_fall, dq28 : 126 read_delay_rise, dq28 : 126 read_delay_fall, dq29 : 138 read_delay_rise, dq29 : 144 read_delay_fall, dq30 : 144 read_delay_rise, dq30 : 138 read_delay_fall, dq31 : 132 read_delay_rise, dq31 : 132 Write DQ Training: write_delay, dq0 : 1147 write_delay, dq1 : 1136 write_delay, dq2 : 1125 write_delay, dq3 : 1136 write_delay, dq4 : 1136 write_delay, dq5 : 1136 write_delay, dq6 : 1125 write_delay, dq7 : 1136 write_delay, dq8 : 1114 write_delay, dq9 : 1114 write_delay, dq10 : 1114 write_delay, dq11 : 1125 write_delay, dq12 : 1125 write_delay, dq13 : 1125 write_delay, dq14 : 1125 write_delay, dq15 : 1125 write_delay, dq16 : 1149 write_delay, dq17 : 1149 write_delay, dq18 : 1160 write_delay, dq19 : 1149 write_delay, dq20 : 1139 write_delay, dq21 : 1139 write_delay, dq22 : 1139 write_delay, dq23 : 1139 write_delay, dq24 : 1141 write_delay, dq25 : 1141 write_delay, dq26 : 1163 write_delay, dq27 : 1141 write_delay, dq28 : 1163 write_delay, dq29 : 1141 write_delay, dq30 : 1141 write_delay, dq31 : 1152 Calibration Registers: CAL_OBS_0: 0x00814756 CAL_OBS_2: 0x00814813 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00147564 CAL_OBS_5: 0x00148138 CAL_OBS_6: 0x00f4756f CAL_OBS_7: 0x03f4813f CS Programmed Delays: phy_grp0_slave_delay_0: 0x033a phy_grp1_slave_delay_0: 0x033a phy_grp2_slave_delay_0: 0x0330 phy_grp3_slave_delay_0: 0x033a phy_grp0_slave_delay_1: 0x0330 phy_grp1_slave_delay_1: 0x033a phy_grp2_slave_delay_1: 0x0330 phy_grp3_slave_delay_1: 0x0330 phy_top_train_calib_error_info: 0x00000000 Training Results; Frequency 1; CS 0 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x26 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x23 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 30b CA Bit 1 delay: 318 CA Bit 2 delay: 31c CA Bit 3 delay: 31d CA Bit 4 delay: 317 CA Bit 5 delay: 33b Write Leveling: DQ Lane 0 WRDQS: 0xba DQ Lane 1 WRDQS: 0xe6 DQ Lane 2 WRDQS: 0xae DQ Lane 3 WRDQS: 0xba DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 290 lat_adj: 6 DQS Gate Lane 1 : slave_delay: 218 lat_adj: 6 DQS Gate Lane 2 : slave_delay: 230 lat_adj: 6 DQS Gate Lane 3 : slave_delay: 194 lat_adj: 6 Read Leveling: read_delay_fall, dq0 : 126 read_delay_rise, dq0 : 138 read_delay_fall, dq1 : 114 read_delay_rise, dq1 : 144 read_delay_fall, dq2 : 126 read_delay_rise, dq2 : 150 read_delay_fall, dq3 : 126 read_delay_rise, dq3 : 156 read_delay_fall, dq4 : 120 read_delay_rise, dq4 : 144 read_delay_fall, dq5 : 120 read_delay_rise, dq5 : 150 read_delay_fall, dq6 : 120 read_delay_rise, dq6 : 132 read_delay_fall, dq7 : 126 read_delay_rise, dq7 : 144 read_delay_fall, dq8 : 126 read_delay_rise, dq8 : 144 read_delay_fall, dq9 : 132 read_delay_rise, dq9 : 156 read_delay_fall, dq10 : 126 read_delay_rise, dq10 : 144 read_delay_fall, dq11 : 120 read_delay_rise, dq11 : 150 read_delay_fall, dq12 : 126 read_delay_rise, dq12 : 144 read_delay_fall, dq13 : 138 read_delay_rise, dq13 : 150 read_delay_fall, dq14 : 120 read_delay_rise, dq14 : 138 read_delay_fall, dq15 : 138 read_delay_rise, dq15 : 150 read_delay_fall, dq16 : 138 read_delay_rise, dq16 : 144 read_delay_fall, dq17 : 150 read_delay_rise, dq17 : 150 read_delay_fall, dq18 : 132 read_delay_rise, dq18 : 126 read_delay_fall, dq19 : 150 read_delay_rise, dq19 : 150 read_delay_fall, dq20 : 132 read_delay_rise, dq20 : 132 read_delay_fall, dq21 : 138 read_delay_rise, dq21 : 138 read_delay_fall, dq22 : 132 read_delay_rise, dq22 : 132 read_delay_fall, dq23 : 126 read_delay_rise, dq23 : 132 read_delay_fall, dq24 : 120 read_delay_rise, dq24 : 114 read_delay_fall, dq25 : 126 read_delay_rise, dq25 : 126 read_delay_fall, dq26 : 132 read_delay_rise, dq26 : 120 read_delay_fall, dq27 : 126 read_delay_rise, dq27 : 126 read_delay_fall, dq28 : 126 read_delay_rise, dq28 : 114 read_delay_fall, dq29 : 132 read_delay_rise, dq29 : 132 read_delay_fall, dq30 : 138 read_delay_rise, dq30 : 126 read_delay_fall, dq31 : 126 read_delay_rise, dq31 : 120 Write DQ Training: write_delay, dq0 : 2047 write_delay, dq1 : 2047 write_delay, dq2 : 2047 write_delay, dq3 : 2047 write_delay, dq4 : 2047 write_delay, dq5 : 2047 write_delay, dq6 : 2047 write_delay, dq7 : 2047 write_delay, dq8 : 2047 write_delay, dq9 : 2047 write_delay, dq10 : 2047 write_delay, dq11 : 2047 write_delay, dq12 : 2047 write_delay, dq13 : 2047 write_delay, dq14 : 2047 write_delay, dq15 : 2047 write_delay, dq16 : 2047 write_delay, dq17 : 2047 write_delay, dq18 : 2047 write_delay, dq19 : 2047 write_delay, dq20 : 2047 write_delay, dq21 : 2047 write_delay, dq22 : 2047 write_delay, dq23 : 2047 write_delay, dq24 : 2047 write_delay, dq25 : 2047 write_delay, dq26 : 2047 write_delay, dq27 : 2047 write_delay, dq28 : 2047 write_delay, dq29 : 2047 write_delay, dq30 : 2047 write_delay, dq31 : 2047 Calibration Registers: CAL_OBS_0: 0x00814756 CAL_OBS_2: 0x00814813 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00147564 CAL_OBS_5: 0x00148138 CAL_OBS_6: 0x00f4756f CAL_OBS_7: 0x03f4813f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0337 phy_grp1_slave_delay_0: 0x0337 phy_grp2_slave_delay_0: 0x0332 phy_grp3_slave_delay_0: 0x0337 phy_grp0_slave_delay_1: 0x032b phy_grp1_slave_delay_1: 0x0337 phy_grp2_slave_delay_1: 0x0332 phy_grp3_slave_delay_1: 0x032b phy_top_train_calib_error_info: 0x00000000 Training Results; Frequency 1; CS 1 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x26 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x23 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 30b CA Bit 1 delay: 318 CA Bit 2 delay: 31c CA Bit 3 delay: 31d CA Bit 4 delay: 317 CA Bit 5 delay: 33b Write Leveling: DQ Lane 0 WRDQS: 0xa2 DQ Lane 1 WRDQS: 0xe4 DQ Lane 2 WRDQS: 0xba DQ Lane 3 WRDQS: 0xb4 DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 48 lat_adj: 7 DQS Gate Lane 1 : slave_delay: 488 lat_adj: 6 DQS Gate Lane 2 : slave_delay: 24 lat_adj: 7 DQS Gate Lane 3 : slave_delay: 500 lat_adj: 6 Read Leveling: read_delay_fall, dq0 : 126 read_delay_rise, dq0 : 150 read_delay_fall, dq1 : 120 read_delay_rise, dq1 : 144 read_delay_fall, dq2 : 126 read_delay_rise, dq2 : 162 read_delay_fall, dq3 : 120 read_delay_rise, dq3 : 156 read_delay_fall, dq4 : 114 read_delay_rise, dq4 : 150 read_delay_fall, dq5 : 114 read_delay_rise, dq5 : 150 read_delay_fall, dq6 : 114 read_delay_rise, dq6 : 144 read_delay_fall, dq7 : 120 read_delay_rise, dq7 : 156 read_delay_fall, dq8 : 126 read_delay_rise, dq8 : 150 read_delay_fall, dq9 : 132 read_delay_rise, dq9 : 156 read_delay_fall, dq10 : 120 read_delay_rise, dq10 : 144 read_delay_fall, dq11 : 132 read_delay_rise, dq11 : 156 read_delay_fall, dq12 : 114 read_delay_rise, dq12 : 144 read_delay_fall, dq13 : 132 read_delay_rise, dq13 : 156 read_delay_fall, dq14 : 114 read_delay_rise, dq14 : 144 read_delay_fall, dq15 : 132 read_delay_rise, dq15 : 156 read_delay_fall, dq16 : 120 read_delay_rise, dq16 : 138 read_delay_fall, dq17 : 150 read_delay_rise, dq17 : 156 read_delay_fall, dq18 : 132 read_delay_rise, dq18 : 144 read_delay_fall, dq19 : 144 read_delay_rise, dq19 : 144 read_delay_fall, dq20 : 132 read_delay_rise, dq20 : 138 read_delay_fall, dq21 : 138 read_delay_rise, dq21 : 138 read_delay_fall, dq22 : 132 read_delay_rise, dq22 : 150 read_delay_fall, dq23 : 132 read_delay_rise, dq23 : 144 read_delay_fall, dq24 : 120 read_delay_rise, dq24 : 120 read_delay_fall, dq25 : 126 read_delay_rise, dq25 : 132 read_delay_fall, dq26 : 126 read_delay_rise, dq26 : 126 read_delay_fall, dq27 : 132 read_delay_rise, dq27 : 138 read_delay_fall, dq28 : 126 read_delay_rise, dq28 : 126 read_delay_fall, dq29 : 138 read_delay_rise, dq29 : 144 read_delay_fall, dq30 : 144 read_delay_rise, dq30 : 138 read_delay_fall, dq31 : 132 read_delay_rise, dq31 : 132 Write DQ Training: write_delay, dq0 : 1152 write_delay, dq1 : 0 write_delay, dq2 : 768 write_delay, dq3 : 1984 write_delay, dq4 : 1280 write_delay, dq5 : 256 write_delay, dq6 : 1216 write_delay, dq7 : 192 write_delay, dq8 : 2047 write_delay, dq9 : 2047 write_delay, dq10 : 2047 write_delay, dq11 : 2047 write_delay, dq12 : 2047 write_delay, dq13 : 2047 write_delay, dq14 : 2047 write_delay, dq15 : 2047 write_delay, dq16 : 2047 write_delay, dq17 : 2047 write_delay, dq18 : 2047 write_delay, dq19 : 2047 write_delay, dq20 : 2047 write_delay, dq21 : 2047 write_delay, dq22 : 2047 write_delay, dq23 : 2047 write_delay, dq24 : 2047 write_delay, dq25 : 2047 write_delay, dq26 : 2047 write_delay, dq27 : 2047 write_delay, dq28 : 2047 write_delay, dq29 : 2047 write_delay, dq30 : 2047 write_delay, dq31 : 2047 Calibration Registers: CAL_OBS_0: 0x00814756 CAL_OBS_2: 0x00814813 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00147564 CAL_OBS_5: 0x00148138 CAL_OBS_6: 0x00f4756f CAL_OBS_7: 0x03f4813f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0337 phy_grp1_slave_delay_0: 0x0337 phy_grp2_slave_delay_0: 0x0332 phy_grp3_slave_delay_0: 0x0337 phy_grp0_slave_delay_1: 0x032b phy_grp1_slave_delay_1: 0x0337 phy_grp2_slave_delay_1: 0x0332 phy_grp3_slave_delay_1: 0x032b phy_top_train_calib_error_info: 0x00000000 DRAM VREF Values: mr12_f1_cs0: 0x00000028 mr12_f1_cs1: 0x0000002b mr12_f1_cs2: 0x00000029 mr12_f1_cs3: 0x0000002a mr12_f2_cs0: 0x00000029 mr12_f2_cs1: 0x0000002b mr12_f2_cs2: 0x00000029 mr12_f2_cs3: 0x0000002a mr14_f1_cs0: 0x00000027 mr14_f1_cs1: 0x00000029 mr14_f1_cs2: 0x00000023 mr14_f1_cs3: 0x00000026 mr14_f2_cs0: 0x00000027 mr14_f2_cs1: 0x00000028 mr14_f2_cs2: 0x00000026 mr14_f2_cs3: 0x00000025 PHY IO Pad TERM Registers: PHY_1320: 0x00014756 PHY_1321: 0x00014756 PHY_1322: 0x00014756 PHY_1323: 0x00014756 PHY_1324: 0x00014756 PHY_1325: 0x00014813 PHY_1326: 0x00014813 PHY_1327: 0x00014756 PHY_1328: 0x00014756 Enhanced Error Reporting: DQS Gate Error: 1 Training Error: 1 FSM Tran Error: 0 PLL Error: 1 Parity Error: 0 Timeout Error: 1 Timeout Error Info: dfi_rddata_valid Timeout: 1 Max PLL lock assertion Timeout: 1 Min PLL lock assertion Timeout: 0 DFI PHY master interface Timeout: 1 dfi_phyupd_req (PI - PHY) Timeout: 1 dfi_phyupd_req (CTL - PHY) Timeout: 0 dfi_lp_ack Timeout: 0 DFS change @ PI - PHY Timeout: 0 DFS change @ CTL -PHY Timeout: 0 CA / CS training Timeout: 0 WRLVL training Timeout: 0 RDGATE training Timeout: 0 RDDATA training Timeout: 0 WDQ training Timeout: 1 Training Error Info: 0x00007800 Data Slice Error Info (bits [4:0]): Byte0: 0x00000102 Byte1: 0x00000102 Byte2: 0x00000102 Byte3: 0x00000102 PLL Frequency Error: 0xf

Also, we have provided the successful training log for a normal booting for reference shown below.

Successful Training log:

SCISERVER Board Configuration header population... PASSED Training Results; Frequency 0; CS 0 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x24 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x26 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x23 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 308 CA Bit 1 delay: 316 CA Bit 2 delay: 31a CA Bit 3 delay: 31a CA Bit 4 delay: 312 CA Bit 5 delay: 338 Write Leveling: DQ Lane 0 WRDQS: 0xba DQ Lane 1 WRDQS: 0xea DQ Lane 2 WRDQS: 0xae DQ Lane 3 WRDQS: 0xba DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 508 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 424 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 448 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 400 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 120 read_delay_rise, dq0 : 144 read_delay_fall, dq1 : 120 read_delay_rise, dq1 : 144 read_delay_fall, dq2 : 132 read_delay_rise, dq2 : 150 read_delay_fall, dq3 : 126 read_delay_rise, dq3 : 156 read_delay_fall, dq4 : 120 read_delay_rise, dq4 : 144 read_delay_fall, dq5 : 120 read_delay_rise, dq5 : 150 read_delay_fall, dq6 : 120 read_delay_rise, dq6 : 138 read_delay_fall, dq7 : 120 read_delay_rise, dq7 : 144 read_delay_fall, dq8 : 126 read_delay_rise, dq8 : 144 read_delay_fall, dq9 : 132 read_delay_rise, dq9 : 156 read_delay_fall, dq10 : 126 read_delay_rise, dq10 : 144 read_delay_fall, dq11 : 120 read_delay_rise, dq11 : 150 read_delay_fall, dq12 : 126 read_delay_rise, dq12 : 144 read_delay_fall, dq13 : 132 read_delay_rise, dq13 : 150 read_delay_fall, dq14 : 126 read_delay_rise, dq14 : 138 read_delay_fall, dq15 : 132 read_delay_rise, dq15 : 150 read_delay_fall, dq16 : 138 read_delay_rise, dq16 : 144 read_delay_fall, dq17 : 150 read_delay_rise, dq17 : 150 read_delay_fall, dq18 : 132 read_delay_rise, dq18 : 132 read_delay_fall, dq19 : 150 read_delay_rise, dq19 : 150 read_delay_fall, dq20 : 132 read_delay_rise, dq20 : 132 read_delay_fall, dq21 : 138 read_delay_rise, dq21 : 138 read_delay_fall, dq22 : 132 read_delay_rise, dq22 : 132 read_delay_fall, dq23 : 126 read_delay_rise, dq23 : 132 read_delay_fall, dq24 : 120 read_delay_rise, dq24 : 114 read_delay_fall, dq25 : 126 read_delay_rise, dq25 : 138 read_delay_fall, dq26 : 132 read_delay_rise, dq26 : 120 read_delay_fall, dq27 : 126 read_delay_rise, dq27 : 126 read_delay_fall, dq28 : 126 read_delay_rise, dq28 : 114 read_delay_fall, dq29 : 126 read_delay_rise, dq29 : 132 read_delay_fall, dq30 : 138 read_delay_rise, dq30 : 126 read_delay_fall, dq31 : 126 read_delay_rise, dq31 : 120 Write DQ Training: write_delay, dq0 : 1157 write_delay, dq1 : 1146 write_delay, dq2 : 1146 write_delay, dq3 : 1146 write_delay, dq4 : 1146 write_delay, dq5 : 1146 write_delay, dq6 : 1146 write_delay, dq7 : 1146 write_delay, dq8 : 1125 write_delay, dq9 : 1136 write_delay, dq10 : 1136 write_delay, dq11 : 1136 write_delay, dq12 : 1136 write_delay, dq13 : 1136 write_delay, dq14 : 1136 write_delay, dq15 : 1147 write_delay, dq16 : 1146 write_delay, dq17 : 1146 write_delay, dq18 : 1146 write_delay, dq19 : 1135 write_delay, dq20 : 1146 write_delay, dq21 : 1135 write_delay, dq22 : 1135 write_delay, dq23 : 1146 write_delay, dq24 : 1163 write_delay, dq25 : 1141 write_delay, dq26 : 1163 write_delay, dq27 : 1163 write_delay, dq28 : 1174 write_delay, dq29 : 1163 write_delay, dq30 : 1163 write_delay, dq31 : 1163 Calibration Registers: CAL_OBS_0: 0x00814756 CAL_OBS_2: 0x00814813 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00147560 CAL_OBS_5: 0x00148138 CAL_OBS_6: 0x00f4756f CAL_OBS_7: 0x03f4813f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0335 phy_grp1_slave_delay_0: 0x0335 phy_grp2_slave_delay_0: 0x0330 phy_grp3_slave_delay_0: 0x0335 phy_grp0_slave_delay_1: 0x0330 phy_grp1_slave_delay_1: 0x0335 phy_grp2_slave_delay_1: 0x0330 phy_grp3_slave_delay_1: 0x0330 phy_top_train_calib_error_info: 0x00000000 Training Results; Frequency 0; CS 1 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x24 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x26 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x23 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 308 CA Bit 1 delay: 316 CA Bit 2 delay: 31a CA Bit 3 delay: 31a CA Bit 4 delay: 312 CA Bit 5 delay: 338 Write Leveling: DQ Lane 0 WRDQS: 0xa2 DQ Lane 1 WRDQS: 0xd2 DQ Lane 2 WRDQS: 0xba DQ Lane 3 WRDQS: 0xba DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 460 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 376 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 436 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 400 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 132 read_delay_rise, dq0 : 150 read_delay_fall, dq1 : 114 read_delay_rise, dq1 : 144 read_delay_fall, dq2 : 132 read_delay_rise, dq2 : 162 read_delay_fall, dq3 : 138 read_delay_rise, dq3 : 156 read_delay_fall, dq4 : 120 read_delay_rise, dq4 : 150 read_delay_fall, dq5 : 120 read_delay_rise, dq5 : 150 read_delay_fall, dq6 : 120 read_delay_rise, dq6 : 144 read_delay_fall, dq7 : 132 read_delay_rise, dq7 : 156 read_delay_fall, dq8 : 132 read_delay_rise, dq8 : 150 read_delay_fall, dq9 : 132 read_delay_rise, dq9 : 156 read_delay_fall, dq10 : 126 read_delay_rise, dq10 : 144 read_delay_fall, dq11 : 132 read_delay_rise, dq11 : 156 read_delay_fall, dq12 : 126 read_delay_rise, dq12 : 144 read_delay_fall, dq13 : 138 read_delay_rise, dq13 : 150 read_delay_fall, dq14 : 126 read_delay_rise, dq14 : 144 read_delay_fall, dq15 : 138 read_delay_rise, dq15 : 150 read_delay_fall, dq16 : 120 read_delay_rise, dq16 : 138 read_delay_fall, dq17 : 150 read_delay_rise, dq17 : 150 read_delay_fall, dq18 : 126 read_delay_rise, dq18 : 138 read_delay_fall, dq19 : 150 read_delay_rise, dq19 : 150 read_delay_fall, dq20 : 126 read_delay_rise, dq20 : 138 read_delay_fall, dq21 : 144 read_delay_rise, dq21 : 138 read_delay_fall, dq22 : 126 read_delay_rise, dq22 : 150 read_delay_fall, dq23 : 132 read_delay_rise, dq23 : 144 read_delay_fall, dq24 : 114 read_delay_rise, dq24 : 126 read_delay_fall, dq25 : 126 read_delay_rise, dq25 : 132 read_delay_fall, dq26 : 126 read_delay_rise, dq26 : 126 read_delay_fall, dq27 : 132 read_delay_rise, dq27 : 144 read_delay_fall, dq28 : 126 read_delay_rise, dq28 : 126 read_delay_fall, dq29 : 138 read_delay_rise, dq29 : 144 read_delay_fall, dq30 : 144 read_delay_rise, dq30 : 138 read_delay_fall, dq31 : 132 read_delay_rise, dq31 : 132 Write DQ Training: write_delay, dq0 : 1142 write_delay, dq1 : 1153 write_delay, dq2 : 1131 write_delay, dq3 : 1131 write_delay, dq4 : 1131 write_delay, dq5 : 1142 write_delay, dq6 : 1142 write_delay, dq7 : 1142 write_delay, dq8 : 1114 write_delay, dq9 : 1125 write_delay, dq10 : 1114 write_delay, dq11 : 1136 write_delay, dq12 : 1125 write_delay, dq13 : 1125 write_delay, dq14 : 1136 write_delay, dq15 : 1136 write_delay, dq16 : 1160 write_delay, dq17 : 1149 write_delay, dq18 : 1160 write_delay, dq19 : 1149 write_delay, dq20 : 1149 write_delay, dq21 : 1139 write_delay, dq22 : 1139 write_delay, dq23 : 1160 write_delay, dq24 : 1146 write_delay, dq25 : 1146 write_delay, dq26 : 1157 write_delay, dq27 : 1146 write_delay, dq28 : 1157 write_delay, dq29 : 1146 write_delay, dq30 : 1146 write_delay, dq31 : 1157 Calibration Registers: CAL_OBS_0: 0x00814756 CAL_OBS_2: 0x00814813 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00147560 CAL_OBS_5: 0x00148138 CAL_OBS_6: 0x00f4756f CAL_OBS_7: 0x03f4813f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0335 phy_grp1_slave_delay_0: 0x0335 phy_grp2_slave_delay_0: 0x0330 phy_grp3_slave_delay_0: 0x0335 phy_grp0_slave_delay_1: 0x0330 phy_grp1_slave_delay_1: 0x0335 phy_grp2_slave_delay_1: 0x0330 phy_grp3_slave_delay_1: 0x0330 phy_top_train_calib_error_info: 0x00000000 Training Results; Frequency 1; CS 0 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x25 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x26 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x24 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 308 CA Bit 1 delay: 315 CA Bit 2 delay: 317 CA Bit 3 delay: 31a CA Bit 4 delay: 312 CA Bit 5 delay: 33b Write Leveling: DQ Lane 0 WRDQS: 0xba DQ Lane 1 WRDQS: 0xe4 DQ Lane 2 WRDQS: 0xae DQ Lane 3 WRDQS: 0xba DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 508 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 424 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 448 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 400 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 120 read_delay_rise, dq0 : 138 read_delay_fall, dq1 : 114 read_delay_rise, dq1 : 144 read_delay_fall, dq2 : 126 read_delay_rise, dq2 : 150 read_delay_fall, dq3 : 126 read_delay_rise, dq3 : 156 read_delay_fall, dq4 : 120 read_delay_rise, dq4 : 144 read_delay_fall, dq5 : 114 read_delay_rise, dq5 : 150 read_delay_fall, dq6 : 120 read_delay_rise, dq6 : 138 read_delay_fall, dq7 : 120 read_delay_rise, dq7 : 144 read_delay_fall, dq8 : 138 read_delay_rise, dq8 : 144 read_delay_fall, dq9 : 132 read_delay_rise, dq9 : 150 read_delay_fall, dq10 : 126 read_delay_rise, dq10 : 144 read_delay_fall, dq11 : 132 read_delay_rise, dq11 : 150 read_delay_fall, dq12 : 126 read_delay_rise, dq12 : 144 read_delay_fall, dq13 : 132 read_delay_rise, dq13 : 150 read_delay_fall, dq14 : 126 read_delay_rise, dq14 : 138 read_delay_fall, dq15 : 138 read_delay_rise, dq15 : 150 read_delay_fall, dq16 : 138 read_delay_rise, dq16 : 144 read_delay_fall, dq17 : 150 read_delay_rise, dq17 : 150 read_delay_fall, dq18 : 132 read_delay_rise, dq18 : 132 read_delay_fall, dq19 : 144 read_delay_rise, dq19 : 150 read_delay_fall, dq20 : 132 read_delay_rise, dq20 : 132 read_delay_fall, dq21 : 138 read_delay_rise, dq21 : 138 read_delay_fall, dq22 : 132 read_delay_rise, dq22 : 132 read_delay_fall, dq23 : 126 read_delay_rise, dq23 : 132 read_delay_fall, dq24 : 120 read_delay_rise, dq24 : 126 read_delay_fall, dq25 : 126 read_delay_rise, dq25 : 132 read_delay_fall, dq26 : 132 read_delay_rise, dq26 : 120 read_delay_fall, dq27 : 126 read_delay_rise, dq27 : 126 read_delay_fall, dq28 : 126 read_delay_rise, dq28 : 114 read_delay_fall, dq29 : 132 read_delay_rise, dq29 : 132 read_delay_fall, dq30 : 132 read_delay_rise, dq30 : 126 read_delay_fall, dq31 : 126 read_delay_rise, dq31 : 120 Write DQ Training: write_delay, dq0 : 1157 write_delay, dq1 : 1146 write_delay, dq2 : 1135 write_delay, dq3 : 1146 write_delay, dq4 : 1146 write_delay, dq5 : 1146 write_delay, dq6 : 1146 write_delay, dq7 : 1146 write_delay, dq8 : 1131 write_delay, dq9 : 1131 write_delay, dq10 : 1136 write_delay, dq11 : 1142 write_delay, dq12 : 1131 write_delay, dq13 : 1142 write_delay, dq14 : 1131 write_delay, dq15 : 1142 write_delay, dq16 : 1152 write_delay, dq17 : 1141 write_delay, dq18 : 1163 write_delay, dq19 : 1141 write_delay, dq20 : 1141 write_delay, dq21 : 1141 write_delay, dq22 : 1141 write_delay, dq23 : 1141 write_delay, dq24 : 1168 write_delay, dq25 : 1146 write_delay, dq26 : 1157 write_delay, dq27 : 1157 write_delay, dq28 : 1168 write_delay, dq29 : 1157 write_delay, dq30 : 1157 write_delay, dq31 : 1163 Calibration Registers: CAL_OBS_0: 0x00814756 CAL_OBS_2: 0x00814813 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00147560 CAL_OBS_5: 0x00148138 CAL_OBS_6: 0x00f4756f CAL_OBS_7: 0x03f4813f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0335 phy_grp1_slave_delay_0: 0x0335 phy_grp2_slave_delay_0: 0x032d phy_grp3_slave_delay_0: 0x0335 phy_grp0_slave_delay_1: 0x032d phy_grp1_slave_delay_1: 0x0335 phy_grp2_slave_delay_1: 0x032d phy_grp3_slave_delay_1: 0x032d phy_top_train_calib_error_info: 0x00000000 Training Results; Frequency 1; CS 1 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x22 DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x25 DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x26 DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x24 ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 308 CA Bit 1 delay: 315 CA Bit 2 delay: 317 CA Bit 3 delay: 31a CA Bit 4 delay: 312 CA Bit 5 delay: 33b Write Leveling: DQ Lane 0 WRDQS: 0xa2 DQ Lane 1 WRDQS: 0xd8 DQ Lane 2 WRDQS: 0xba DQ Lane 3 WRDQS: 0xba DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 460 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 376 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 436 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 400 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 132 read_delay_rise, dq0 : 150 read_delay_fall, dq1 : 120 read_delay_rise, dq1 : 144 read_delay_fall, dq2 : 132 read_delay_rise, dq2 : 162 read_delay_fall, dq3 : 138 read_delay_rise, dq3 : 156 read_delay_fall, dq4 : 126 read_delay_rise, dq4 : 150 read_delay_fall, dq5 : 120 read_delay_rise, dq5 : 150 read_delay_fall, dq6 : 120 read_delay_rise, dq6 : 144 read_delay_fall, dq7 : 132 read_delay_rise, dq7 : 156 read_delay_fall, dq8 : 132 read_delay_rise, dq8 : 150 read_delay_fall, dq9 : 132 read_delay_rise, dq9 : 156 read_delay_fall, dq10 : 126 read_delay_rise, dq10 : 144 read_delay_fall, dq11 : 132 read_delay_rise, dq11 : 150 read_delay_fall, dq12 : 126 read_delay_rise, dq12 : 144 read_delay_fall, dq13 : 138 read_delay_rise, dq13 : 150 read_delay_fall, dq14 : 126 read_delay_rise, dq14 : 144 read_delay_fall, dq15 : 138 read_delay_rise, dq15 : 150 read_delay_fall, dq16 : 120 read_delay_rise, dq16 : 138 read_delay_fall, dq17 : 150 read_delay_rise, dq17 : 150 read_delay_fall, dq18 : 126 read_delay_rise, dq18 : 138 read_delay_fall, dq19 : 144 read_delay_rise, dq19 : 150 read_delay_fall, dq20 : 132 read_delay_rise, dq20 : 138 read_delay_fall, dq21 : 138 read_delay_rise, dq21 : 138 read_delay_fall, dq22 : 126 read_delay_rise, dq22 : 150 read_delay_fall, dq23 : 132 read_delay_rise, dq23 : 144 read_delay_fall, dq24 : 114 read_delay_rise, dq24 : 126 read_delay_fall, dq25 : 132 read_delay_rise, dq25 : 132 read_delay_fall, dq26 : 126 read_delay_rise, dq26 : 126 read_delay_fall, dq27 : 132 read_delay_rise, dq27 : 138 read_delay_fall, dq28 : 126 read_delay_rise, dq28 : 126 read_delay_fall, dq29 : 138 read_delay_rise, dq29 : 144 read_delay_fall, dq30 : 138 read_delay_rise, dq30 : 138 read_delay_fall, dq31 : 132 read_delay_rise, dq31 : 132 Write DQ Training: write_delay, dq0 : 1152 write_delay, dq1 : 1153 write_delay, dq2 : 1131 write_delay, dq3 : 1141 write_delay, dq4 : 1131 write_delay, dq5 : 1153 write_delay, dq6 : 1142 write_delay, dq7 : 1153 write_delay, dq8 : 1114 write_delay, dq9 : 1125 write_delay, dq10 : 1125 write_delay, dq11 : 1136 write_delay, dq12 : 1125 write_delay, dq13 : 1125 write_delay, dq14 : 1125 write_delay, dq15 : 1136 write_delay, dq16 : 1163 write_delay, dq17 : 1152 write_delay, dq18 : 1163 write_delay, dq19 : 1152 write_delay, dq20 : 1141 write_delay, dq21 : 1141 write_delay, dq22 : 1141 write_delay, dq23 : 1141 write_delay, dq24 : 1146 write_delay, dq25 : 1146 write_delay, dq26 : 1157 write_delay, dq27 : 1168 write_delay, dq28 : 1157 write_delay, dq29 : 1146 write_delay, dq30 : 1146 write_delay, dq31 : 1157 Calibration Registers: CAL_OBS_0: 0x00814756 CAL_OBS_2: 0x00814813 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00147560 CAL_OBS_5: 0x00148138 CAL_OBS_6: 0x00f4756f CAL_OBS_7: 0x03f4813f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0335 phy_grp1_slave_delay_0: 0x0335 phy_grp2_slave_delay_0: 0x032d phy_grp3_slave_delay_0: 0x0335 phy_grp0_slave_delay_1: 0x032d phy_grp1_slave_delay_1: 0x0335 phy_grp2_slave_delay_1: 0x032d phy_grp3_slave_delay_1: 0x032d phy_top_train_calib_error_info: 0x00000000 DRAM VREF Values: mr12_f1_cs0: 0x00000028 mr12_f1_cs1: 0x0000002c mr12_f1_cs2: 0x00000029 mr12_f1_cs3: 0x00000029 mr12_f2_cs0: 0x00000029 mr12_f2_cs1: 0x0000002c mr12_f2_cs2: 0x00000029 mr12_f2_cs3: 0x0000002a mr14_f1_cs0: 0x00000027 mr14_f1_cs1: 0x0000002b mr14_f1_cs2: 0x00000027 mr14_f1_cs3: 0x00000028 mr14_f2_cs0: 0x0000002a mr14_f2_cs1: 0x0000002b mr14_f2_cs2: 0x00000025 mr14_f2_cs3: 0x00000028 PHY IO Pad TERM Registers: PHY_1320: 0x00014756 PHY_1321: 0x00014756 PHY_1322: 0x00014756 PHY_1323: 0x00014756 PHY_1324: 0x00014756 PHY_1325: 0x00014813 PHY_1326: 0x00014813 PHY_1327: 0x00014756 PHY_1328: 0x00014756 Enhanced Error Reporting: DQS Gate Error: 0 Training Error: 0 FSM Tran Error: 0 PLL Error: 0 Parity Error: 0 Timeout Error: 0 PLL Frequency Error: 0x0

In summary, there are below 2 methods seem could improve the results.

1: Decrease the frequency to 3200Mb/s.

2: Increase VDD1 from 1.8V to 1.85V and increase VDD2 from 1.1V to 1.15V.

As you know, we still need to find the root cause of this problem, so we may need hear some feedback based on our experiment results, thanks!

Also, based on our log, could you find any useful information that could help us debug?

Thanks a lot!

Kevin