Hi Ti,

after PSDK RTOS Update from v09_00 to v09_01 all our R5 applications did not work anymore.

More specific, the R5 cores entered "prefetch exception" state after configuring and activating MPU unit.

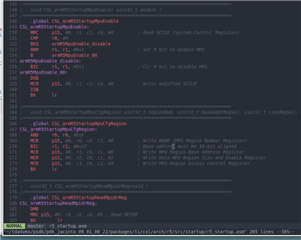

After rereading documentation, and poking around source-code this changeset grabbed my attention:

Left is v09_00, right is v09_01: pdk_jacinto*/packages/ti/csl/arch/r5/startup.c

Line 150, 153 on right side: accessCtrlRegVal is set differently. gMemAttr did not change, so for me it seems quite obvious that existing MPU-Configurations will break.

Could you explain please that change? And why is that not documented?

Thank you, and best regards,

Thomas