Other Parts Discussed in Thread: SK-AM62B-P1, SK-AM64B, SK-AM62A-LP, SYSCONFIG

Hi Sir,

We have three boards on hand:

SK-AM62B-P1

SK-AM64B

SK-AM62A-LP

How can I find the Mode Register setting or table?

Thanks.

Best regards,

Maurs

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Sir,

We have three boards on hand:

SK-AM62B-P1

SK-AM64B

SK-AM62A-LP

How can I find the Mode Register setting or table?

Thanks.

Best regards,

Maurs

Hi Sir,

Yes this is related to DDR.

I need the MR table for DDR4 and LPDDR4.

Thanks.

Best regards,

Maurs

Thank you, Maurice. I have assigned the thread to the DDR expert. You should get a response by EOD.

Hi James,

We are still trying to boot up EVM on hand, but we'd like to clarify some tables in TRM first.

AM64x TRM for example, what are the different above these registers for MR0?

8.1.5.255 CTLPHY_WRAP__CTL_CFG__CTLCFG_DDR16SS_DENALI_CTL_204 Registers

8.1.5.267 CTLPHY_WRAP__CTL_CFG__CTLCFG_DDR16SS_DENALI_CTL_216 Registers

8.1.5.771 CTLPHY_WRAP__CTL_CFG__CTLCFG_DDR16SS_DENALI_PI_297 Registers

8.1.5.803 CTLPHY_WRAP__CTL_CFG__CTLCFG_DDR16SS_DENALI_PI_329 Registers

Maurice, the controller has multiple registers for different frequency sets and chip selects. CTL_204 has MR0 data for freq set 0, CS0, and CTL_216 has MR0 data for freq set 1, CS1. Similarly, the PI (PHY Interface), which is involved in training, has similar sets of registers.

Do you have a JTAG pod with the boards? Or just trying to boot an SDK image using UART console? If you can provide a full register dump using Code Composer, i can help parse the information to get what you need.

Regards,

James

Hi James,

How can we get the full register dump by CCS?

We are trying to boot an SDK image using UART console but stuck in somewhere.

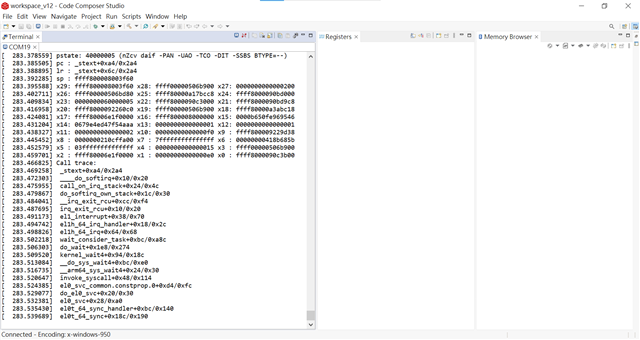

As you can see, the register and memory browser are empty.

Or should I just paste the UART log in here?

Another question, is there a table for "freq set 0/1/2" stand for?

Thanks.

B.R,

Maurice

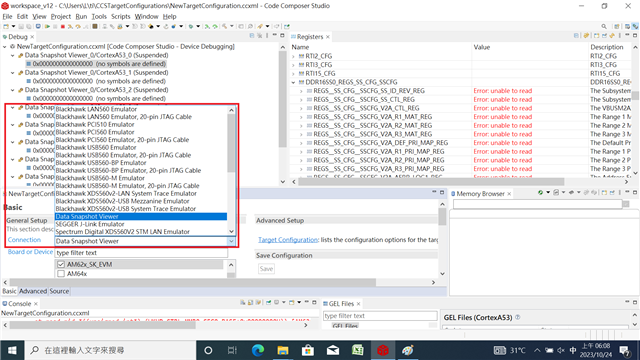

To get a full register dump by CCS:

-create a new Target Configuration and choose the appropriate board in "Board or Device"

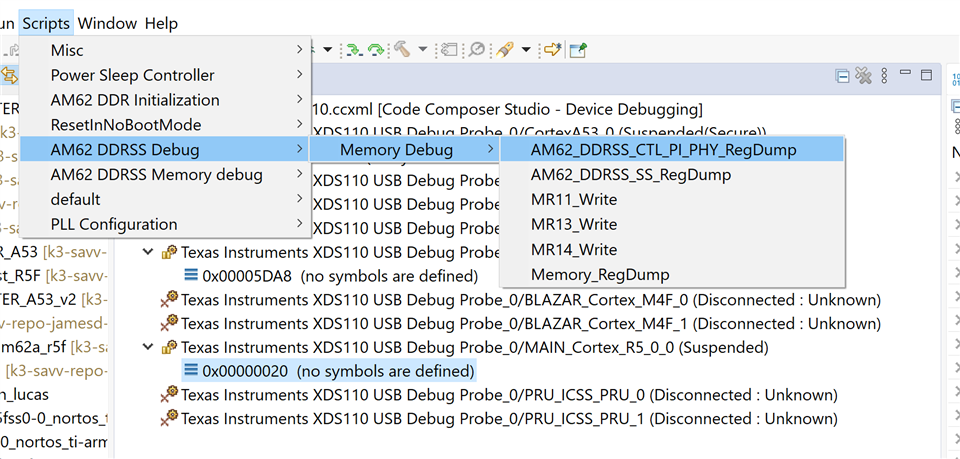

-after powering up the board, connect to R5 core and run AM62 DDRSS Debug->Memory Debug->AM62_DDRSS_CTL_PI_PHY_RegDump

This should output all relevant registers to the console window. Post these here and i can help parse them for you

As for the frequency sets, F0 is the boot frequency, and F1/F2 are the operating frequencies. Currently, our SDKs only use one operating frequency F2.

Regards,

james

Hi James,

We cannot find the appropriate board in "Board or Device" or "Connection".

Here're the boards on hand:

SK-AM62A-LP

SK-AM62B-P1

SK-AM64B

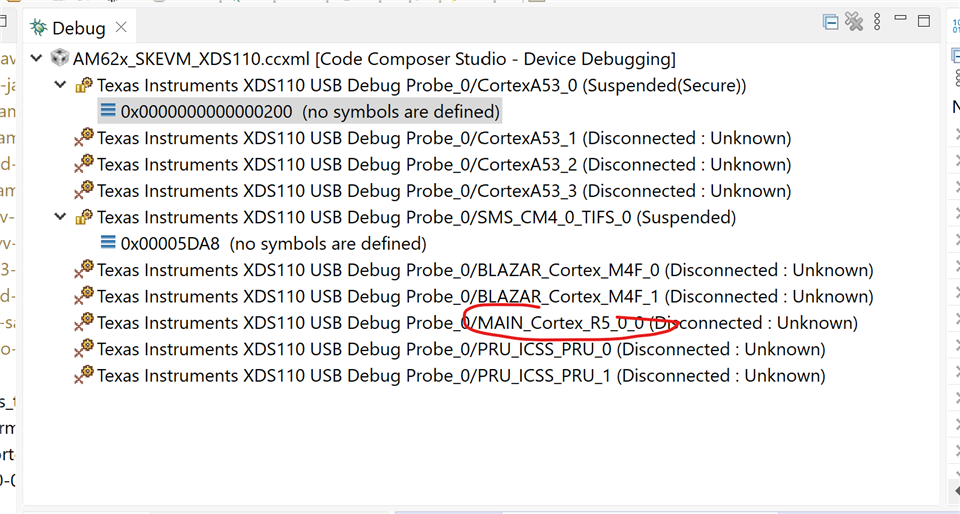

So, what F0/1/2 frequencies are?

Are they 50/800/800 MHz in below pic (SysConfig LP4)?

Then how about DDR4?

Thanks.

Maurice

For SK-AM64B, choose AM64x_SK_EVM

For SK-AM62B-P1, choose AM62x_SK_EVM

For SK-AM62A-LP, choose AM62A_SK_EVM

AM64x and AM62x will run at 800MHz, AM62Ax will run at 1600MHz. Only FSP2 is used, FSP1 is not used, FSP0 boot frequency will always be 50MHz

Regards,

James

Hi James,

Thanks for the reply.

I can see device in the list, but still don't know which connection I shoule select.

As below pic.

Also, does "connect to R5 core" mean to connect UART with the 4th USB serial port?

And where can I run "AM62 DDRSS Debug->Memory Debug->AM62_DDRSS_CTL_PI_PHY_RegDump" in CCS window?

Thanks.

Maurice

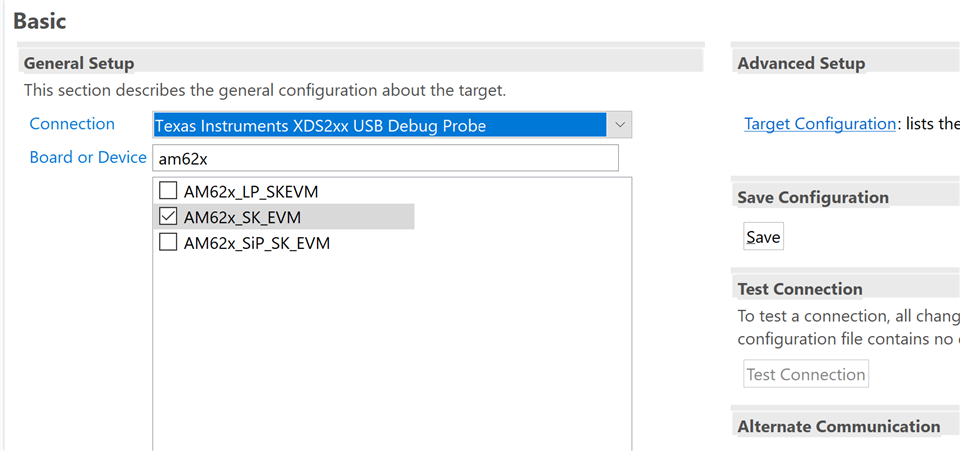

Maurice, what type of JTAG pod do you have? That's what you would choose in the device list For example, here i'm using the TI XDS200 probe:

You will see cortex_R5 as one of the cores to connect to.

Once connected, you can run the script in CCS.

Regards,

James