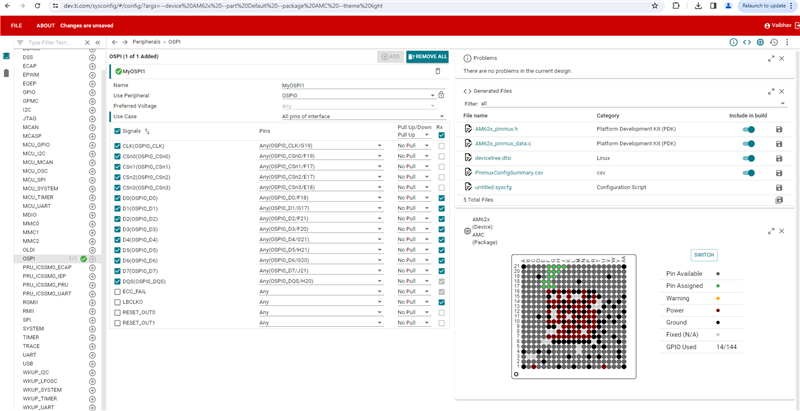

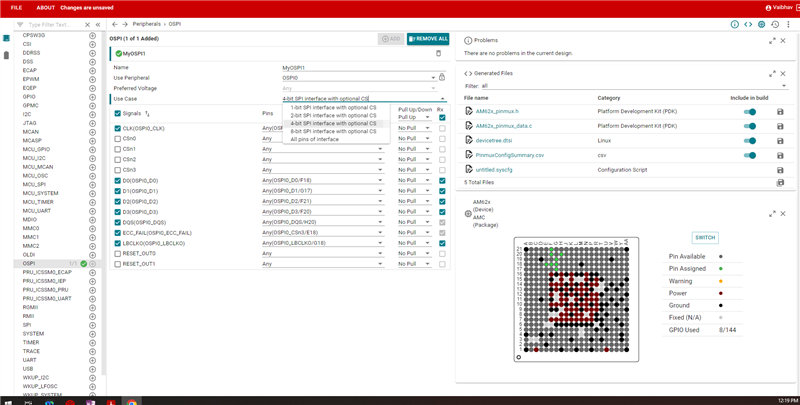

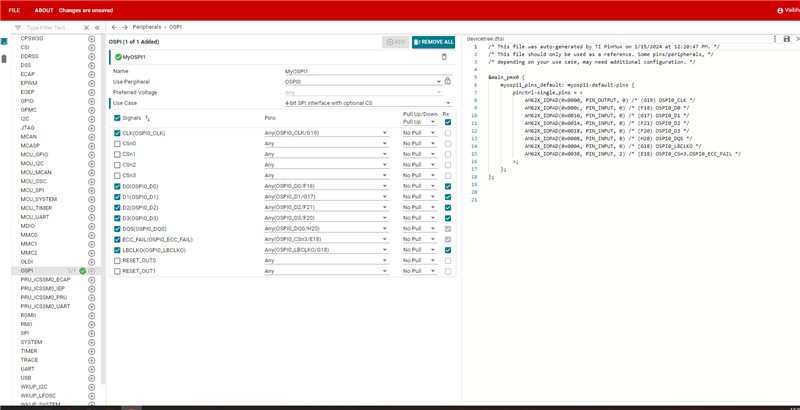

Part Number: AM625

Other Parts Discussed in Thread: SYSCONFIG

Dear Team,

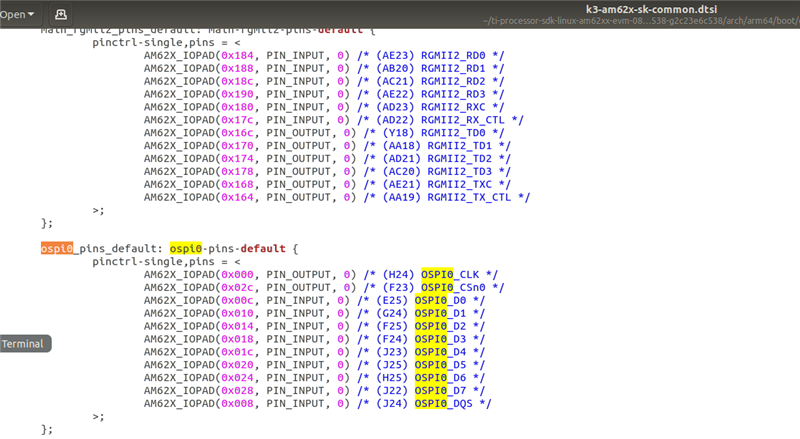

In the AM62x SDK [v9.1], is it necessary to modify the file ..arch/arm/dts/k3-am62x-sk-common.dtsi for a custom design of the SoM?

If modification is required, which node should I start with in the dts file?

Thanks and Regards,

Ravikumar