Hi Team,

1)

if we use XFI/USXGMII interface on SERDES2 AM69A do we need to supply 156.25MHz clock to the SERDES2_REFCLK_x pins?

2)

Or is there internal clock of 156.25MHz from PLL3 that can be used?

3)

if there is an internal PLL that outputs 156.25MHz clock, can we output this clock on the SERDES2_REFCLK_x pins and rout them to our device?

4)

what is the default setting of SERDES2_REFCLK_x pins (input or output) , and how to set them to output?

5)

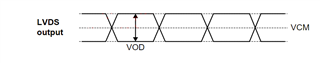

when the clock is outputted on SERDES2_REFCLK_x pins where can we find the electrical specification of this clock?

Best Regards,

d.