Other Parts Discussed in Thread: SYSCONFIG

Hi,

My customer is trying to use BCDMA on A53 core with RTOS SDK.

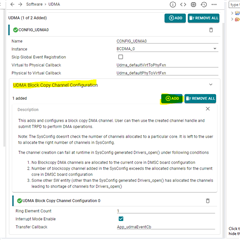

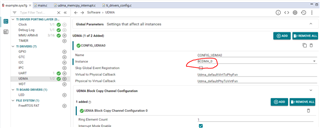

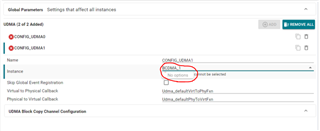

SDK provides examples and it uses BCDMA channel#0. Please see below sysconfig snapshot.

The customer wants to use other than channel#0, for example channel#1, but sysconfig does not have such option.

When they manually modify the Instance to "BCDMA_1", GUI says "No Options".

Is there any way to use BCDMA channels other than channel#0?

Thanks and regards,

Koichiro Tashiro