Hi,TI

We want to use LPM to enter MCU-only mode.

SDK:08_06_00_12

board: TDA4VM EVM

1 We want to start MCU Domain and MAIN Domain by spl. So need porting LPM to MCU1_0, what do we need to do?

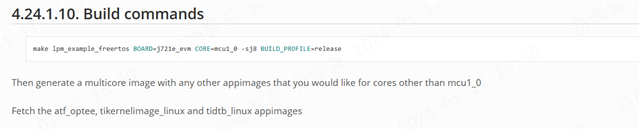

2 in 4.24.1. MCU Only mode — Platform Development Kit (PDK) - JACINTO User Guide (ti.com), where to fetch the atf_optee, tikernelimage_linux and tidtb_linux appimages? Is there an environment to verify it?

Best Rgards,

Zhang