Other Parts Discussed in Thread: SYSCONFIG

Hi,

Q1

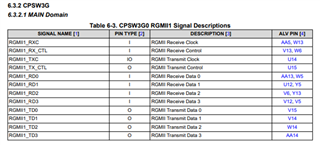

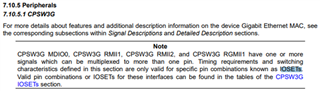

In the data sheet, RGMII is described as having multiple PINs MUXed together. However, another page provides definitions for combinations of use. Are port combinations other than IOSET in the data sheet not configurable? For example, is it possible to configure a combination like PRG0_PRU1_GPO7, RGMII1_RD1, PRG1_PRU1_GPO8 in RGMII1_RD0?

Q2.

Is there a register to set IOSET other than I/O pin port settings?

Situation

・Unable to communicate via TCP/IP

・Ethernet is configured with RGMII1 and PHY (DP83867IRRGZ)

・Ethernet is linked up

・When I observed the packet, broadcast etc. could be sent.

・When I checked with an oscilloscope, the data has reached the inside of the PHY (RXD* of RGMII)

Thanks,

Conor