Hi,TI

Now we found phy error on our TDA4VM board. The log as follows:

[MCU2_0] 52.764888 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 52.765145 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 52.765498 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 52.765773 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 52.863684 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 52.863961 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 52.864224 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 52.864592 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 52.864867 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 52.865125 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 52.865473 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 52.865756 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 52.963687 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 52.963965 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 52.964220 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 52.964585 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 52.964859 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 52.965122 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 52.965375 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 52.965745 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.063687 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.063972 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.064236 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.064610 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.064890 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.065151 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.065506 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.065783 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.163683 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.163968 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.164232 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.164603 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.164880 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.165141 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.165498 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.165773 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.263691 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.263977 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.264237 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.264606 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.264880 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.265141 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.265500 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.265780 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.363690 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.363971 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.364232 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.364599 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.364872 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.365131 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.365483 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.365763 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.463683 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.463963 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.464222 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.464590 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.464866 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.465126 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.465471 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.465758 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.563685 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.563966 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.564225 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.564597 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.564871 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.565127 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.565473 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.565753 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.663686 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.663968 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.664231 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.664607 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.664880 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.665144 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.665500 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.665775 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.763688 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.763973 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.764241 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.764608 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.764884 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.765144 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.765502 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.765777 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.863686 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.863965 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.864221 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.864591 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.864867 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.865124 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.865470 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.865755 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 53.963688 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 53.963969 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 53.964228 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 53.964587 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 53.964865 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 53.965128 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 53.965474 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 53.965758 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 54.063683 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 54.063967 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 54.064227 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 54.064602 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 54.064878 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 54.065140 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 54.065498 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 54.065774 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 54.163685 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 54.163967 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 54.164229 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 54.164593 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 54.164873 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 54.165135 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 54.165492 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 54.165771 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 54.263691 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 54.263978 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 54.264240 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 54.264610 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 54.264889 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 54.265147 s: EnetPhy_enableState: PHY 18: no supported caps found [MCU2_0] 54.265505 s: EnetPhy_enableState: PHY 19: no supported caps found [MCU2_0] 54.265785 s: EnetPhy_enableState: PHY 15: no supported caps found [MCU2_0] 54.363685 s: EnetPhy_enableState: PHY 12: no supported caps found [MCU2_0] 54.363964 s: EnetPhy_enableState: PHY 16: no supported caps found [MCU2_0] 54.364219 s: EnetPhy_enableState: PHY 0: no supported caps found [MCU2_0] 54.364589 s: EnetPhy_enableState: PHY 3: no supported caps found [MCU2_0] 54.364863 s: EnetPhy_enableState: PHY 17: no supported caps found [MCU2_0] 54.365125 s: EnetPhy_enableState: PHY 18: no supported c

The SDK: 08_06_00_12

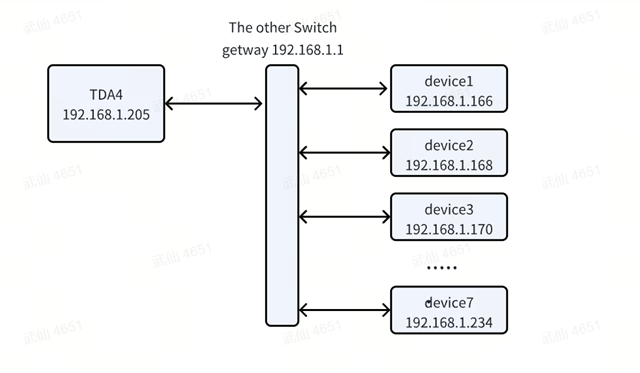

The eth board: Refer to GESI

It is normal at the beginning and abnormal after running for a period of time. Can you give us some advice?

Best Regards,

Zhang