Other Parts Discussed in Thread: SYSCONFIG

I was generating some new DDR4 configs and noticed some unexpected register changes. Below is the comparison with our existing 2GB module, which matches the EVM. Could you explain what the changes are?

I looked at the release notes for the sysconfig tool but none of this was mentioned. www.ti.com/.../1.19.0.3426

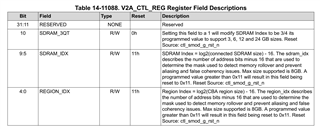

$ diff ~/local/u-boot-mitysom-62x/arch/arm/dts/k3-am62x-sk-ddr4-1600MTs.dtsi mitysom_am62_2GB_DDR4.dtsi -u --- /home/jcormier/local/u-boot-mitysom-62x/arch/arm/dts/k3-am62x-sk-ddr4-1600MTs.dtsi 2024-01-25 15:17:50.420051584 -0500 +++ mitysom_am62_2GB_DDR4.dtsi 2024-01-25 15:08:28.848609782 -0500 @@ -1,17 +1,19 @@ // SPDX-License-Identifier: GPL-2.0+ /* * This file was generated with the - * AM62x SysConfig DDR Subsystem Register Configuration Tool v0.09.09 - * Fri Oct 27 2023 11:47:38 GMT-0400 (Eastern Daylight Time) + * AM62x SysConfig DDR Subsystem Register Configuration Tool v0.10.01 + * Thu Jan 25 2024 15:04:00 GMT-0500 (Eastern Standard Time) * DDR Type: DDR4 * Frequency = 800MHz (1600MTs) * Density: 16Gb * Number of Ranks: 1 */ + #define DDRSS_PLL_FHS_CNT 6 #define DDRSS_PLL_FREQUENCY_1 400000000 #define DDRSS_PLL_FREQUENCY_2 400000000 +#define DDRSS_SDRAM_IDX 15 #define DDRSS_CTL_0_DATA 0x00000A00 @@ -608,10 +610,10 @@ #define DDRSS_PI_168_DATA 0x0000003A #define DDRSS_PI_169_DATA 0x0004003A #define DDRSS_PI_170_DATA 0x04000400 -#define DDRSS_PI_171_DATA 0xC8040009 +#define DDRSS_PI_171_DATA 0x68040009 #define DDRSS_PI_172_DATA 0x0400091C -#define DDRSS_PI_173_DATA 0x00091CC8 -#define DDRSS_PI_174_DATA 0x001CC804 +#define DDRSS_PI_173_DATA 0x00091C68 +#define DDRSS_PI_174_DATA 0x001C6804 #define DDRSS_PI_175_DATA 0x00000118 #define DDRSS_PI_176_DATA 0x00001860 #define DDRSS_PI_177_DATA 0x00000118