Other Parts Discussed in Thread: SK-AM68, , CCSTUDIO

Dear TI,

I'm using AM68A HS-FS chip on my custom board(I have SK-AM68 both),using the ti-processor-sdk-rtos-j721s2-evm-09_01_00_06.

I follow the steps to setup CCS:ti-processor-sdk-rtos-j721s2-evm-09_00_01_01-docs_only/pdk_j721s2_09_00_01_04/docs/userguide/j721s2/ccs_setup_j721s2.html

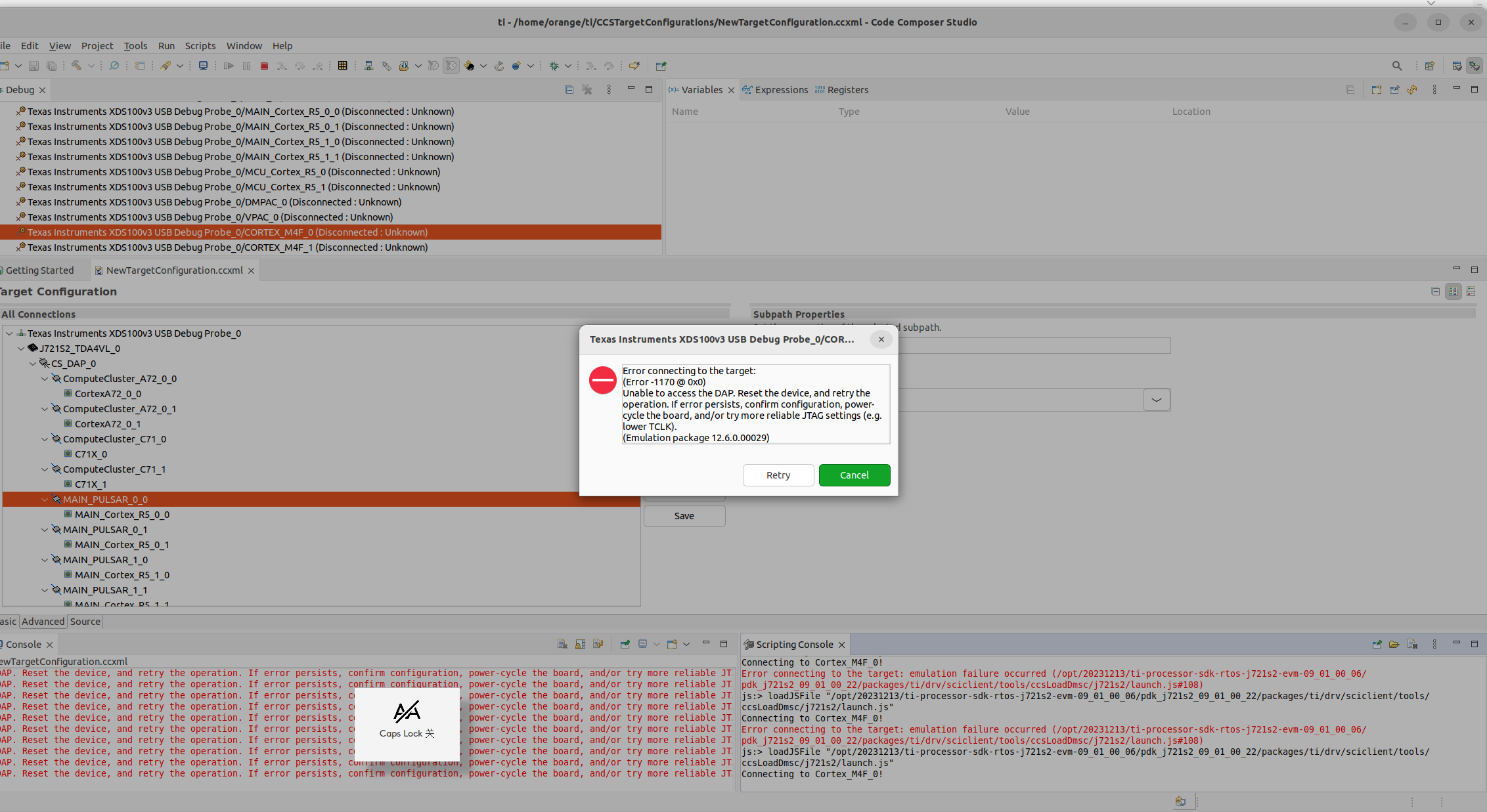

it would be faild to connect to M4F

I've changed the pdk path in launch.js, here is the js file. So how can I connect the HS-FS device with JTAG in CCS.