Part Number: TDA4VM

Hi experts,

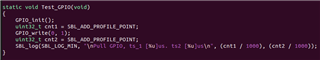

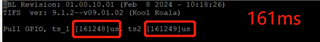

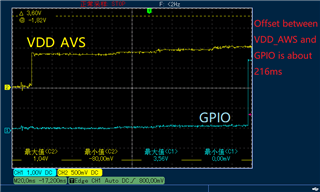

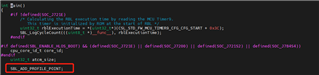

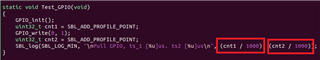

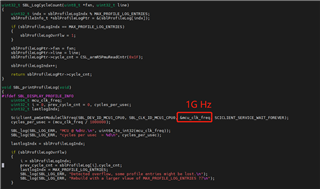

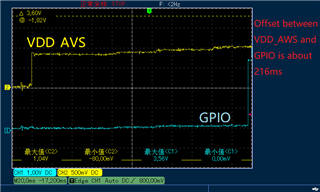

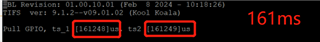

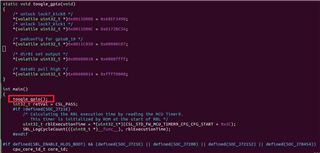

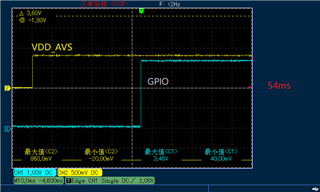

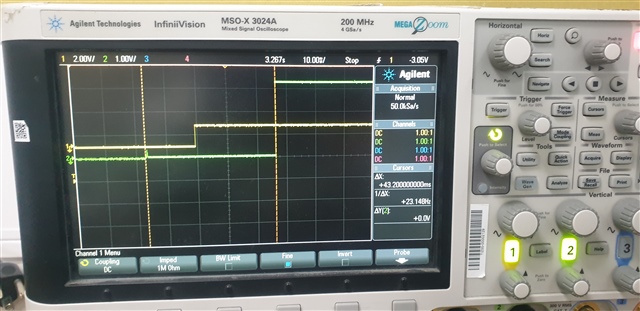

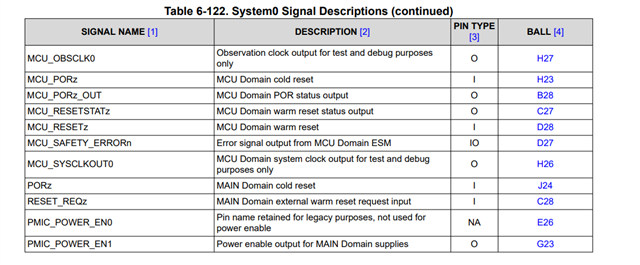

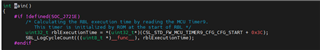

I have a probelm when I try to evaluate boot time under different boot modes of TDA4VM. When I look into RTOS SDK, I notice that there's a way to calculate the execution of RBL(ROM BootLoader) stage. But platform J721E is excluded in the code as shown in snapshot below.

I wonder why this operation does not apply to platform J721E? And is there any other way to evaluate the execution time of RBL for TDAVM?

Best Regards