Hello

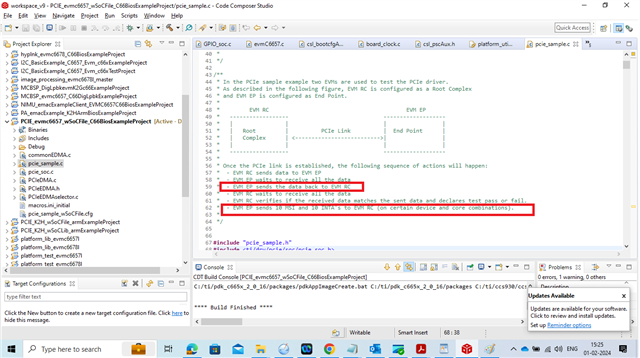

I am using two EVM's (TMS320c6657) communicating using PCIE.

I was able to read and write using EDMA in both sizes, now I want to test write using cpu.

write from root complex to endpoint : OK but i couldn't write the other way: endpoint --> root complex : KO

is there some special configuration to be able to write from endpoint to root complex?

thanks