Dear TI

Our latest PCBA use XJ784S45AALY-HS-SE-FS for eFuse programing,found several Soc cannot boot from ospi , there is no data and clk waveform about ospi when power on,

attempted to make some modifications as below。

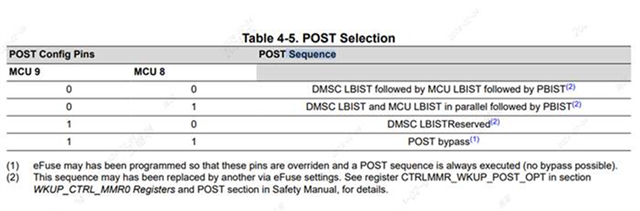

MCU[9:8] 11 , can boot;

MCU[9:8] 01 , cannot boot;

MCU[9:8] 00 , can boot;

According to the specification,MCU[9:8] are the POST config pins,

What's the reason for the above.

Which POST sequence we should use ,what determines the configuration of MCU[9:8]。

thanks