Hi,

My customer reported an issue related to PCIe.

In their system, PCIe is connected to an external USB controller.

During system setup phase, firmware is download to the USB controller iva PCIe.

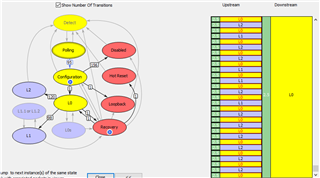

The sequence is like below.

Please note;

- Port U13 is just a gpio output for debug.

- software waits(2sec or 1sec) are added in each steps just for debug purpose

The link down happens at "FW download" step in above figure once in 10 to 30 times trials.

If FW download finishes successfully, no issue happens after that.

I know this is very vague question, but do you have any points should be checked?

Did you have similar issue before?

Thanks and regards,

Koichiro Tashiro

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.