Other Parts Discussed in Thread: DP83826E

Hello Champs,

HW: PHY 83826E

SW: mcu_plus_sdk_am64x_09_00_00_31

Hardware connection:

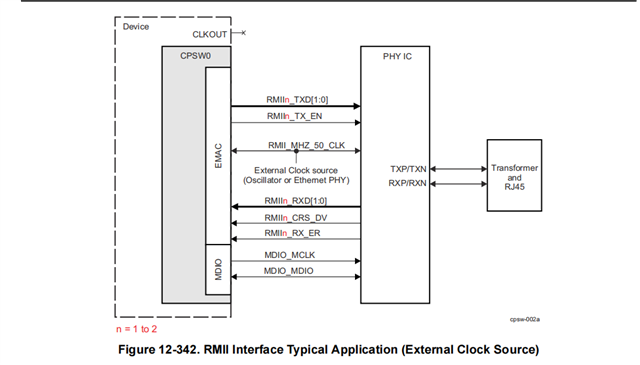

CPSW MAC ENT PORT1 is connected to 83826E as RMII SLAVE MODE, external crystal 50M is connected AM6442 to AA5 pin (i.e. RMII_MHZ_50_CLK) and 83826 pin 9

Testing:

By reading the PHY register 0x468, it shows that the PHY is operating with RMII SLAVE MODE, and read the register 0x10, he PHY is in the 100M full-duplex link state.

Problems encountered:

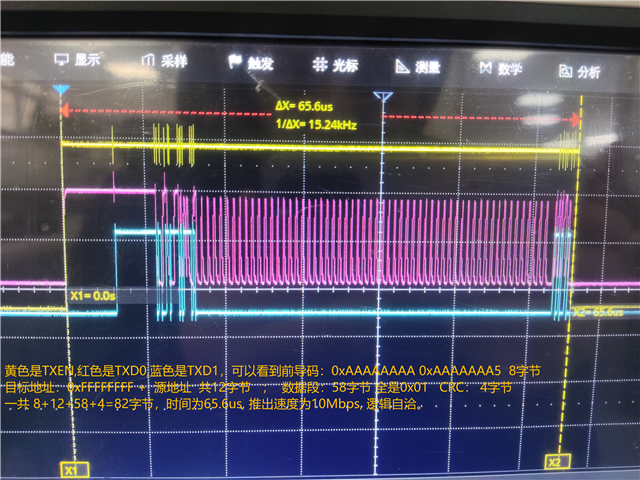

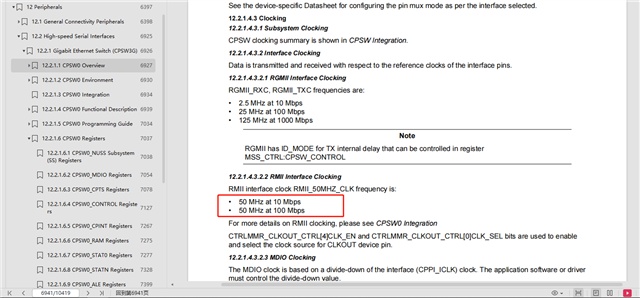

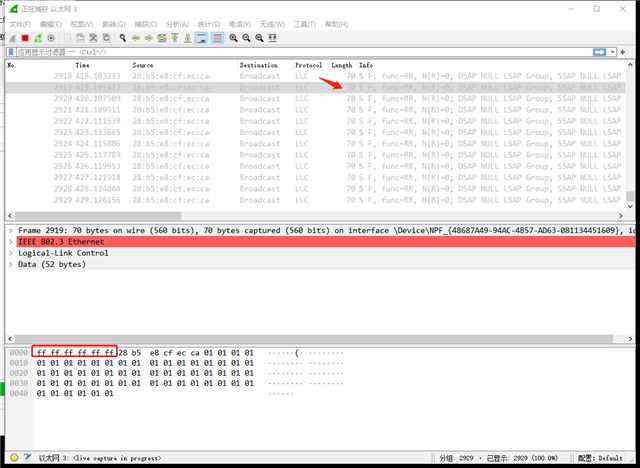

Forward data to ENT PORT1 via CPSW CPPI for Ethernet frame data transmission. Use the oscilloscope to catch PHY Chip Pin 23 (TXEN) PHY Chip Pin 24 (TXD0) PHY Chip Pin 25 (TXD1) and see the Ethernet Frame Preamble, Destination Address, Source Address, Random data, CRC (total 82 bytes), TXEN pulse width 65.6us, i.e. speed 10Mbps.

Customer guesses the ENT PORT1 sends only 10M. But he couldn't find the right configuration to change it to 100M.

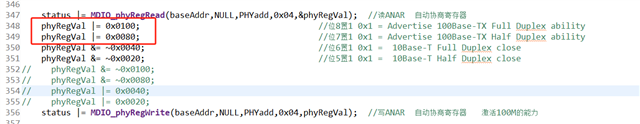

The current CPSW speed-related configurations are as follows: (Are there any other configurations that can set the port speed?)

Set register (0x08022330) bit7 to 0:10/100 mode ; bit17 is 0: does not force into Gigabit

Customer is using the project based on C:\ti\mcu_plus_sdk_am64x_09_00_31\examples\networking\enet_layer2_cpsw\am64x-evm. The RGMII mode can run on EVM. But in the project and the hardware board, what is needed is the RMII mode, so he modified some of the configuration to fit the RMII mode.

①

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, 1); //偏移量为4044,因此它落在分区1

*(vuint32_t*)(0x43004044) = 1; //cpsw0-port1 2选择RGMII 1选择RMII

*(vuint32_t*)(0x43004048) = 1; //cpsw0-port2 2选择RGMII 1选择RMII

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, 1);

② set (0x08022330) bit7 为 0:10/100 mode ; bit17 为 0:不强制进入千兆

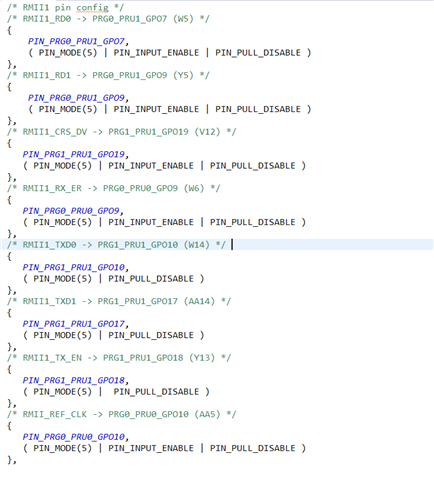

③ configure RMII:

Thanks

Regards

Shine