Dear team,

I am evaluating the RS485 over UART5 module on R5 core of starter kit. As of now i have imported UART example from MCU+SDL v9.1.00.41 and one more UART peripheral is added (ie. UART5) for RS485.

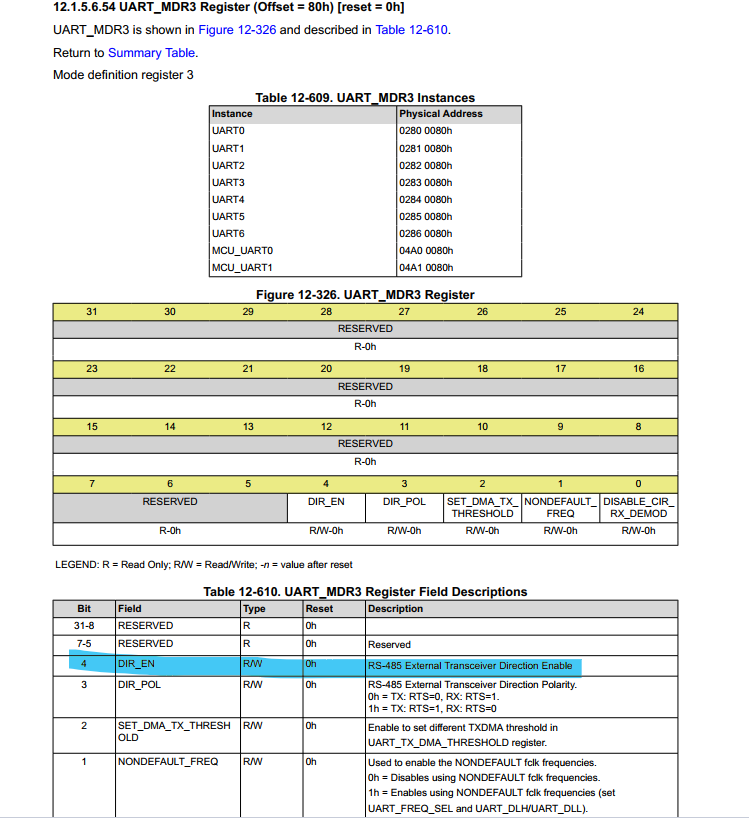

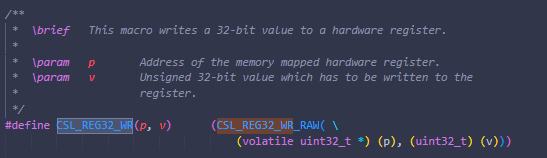

In TRM it is mentioned that to select a RS-485 mode, we need to set the UART_MDR3[4] DIR_EN bit field to 0x1 but if i check in low level driver files I am not getting any specific APIs to change the UART_MDR3 mem registers of UART.

How should we configure the UART for RS485 to work.

Thanks

Shraddha