Part Number: DRA829V

Other Parts Discussed in Thread: DRA829

We are using the two recommended PMICs TPS65941213-Q1 and TPS65941111-Q1 running them according to pdn-0C. https://www.ti.com/lit/ug/slvuc99a/slvuc99a.pdf?ts=1709827472401

According to DRA829 datasheet power down should look like this:

And according to PDN-0C the PMIC should power down according to:

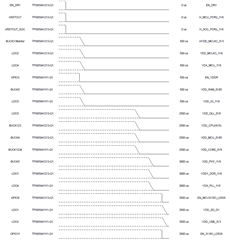

I measure the following:

| D0 | VSYS_MCUIO_3V3 |

| D1 | VSYS_IO_3V3 |

| D2 | VSYS_IO_1V8 |

| D3 | VDA_MCU_1V8 |

| D4 | VDA_PLL_1V8 |

| D5 | VDD_PHYIO_1V8 |

| D6 | VDD_MCU_0V85 |

| D7 | VDD_CPU_AVS |

| D8 | VDA_DLL_0V8 |

| D9 | VDD_CORE_0V8 |

| D10 | VDD_CORE_RAM_0V85 |

| D11 | VDD_DDR_1V1 |

| D12 | PMIC_EN |

| D13 | MCU_PORz |

Most of the rails power down as intended. However VDA_DLL_0V8 (3.77ms), VDA_MCU_1V8 (4.03m) and VDA_PLL_1V8 (3.87ms) does not power down at the correct timestamp.

They all power down after VSYS_MCUIO_3V3 and VSYS_IO_3V3 which should be the last two powersupplys to ramp down.

The rails are connected from the PMICs according to PDN-0C.

We have a help processor pulling MCU_PORz low first, and then PMIC_EN low.