Part Number: TDA4VM

Hi there,

For MCRC there are two PSA signature registers (low and high).

How do I have to handle this two registers. Can you give me an example ?

For example how do I have to calculate a checksum over 16 bytes of data in full CPU mode:

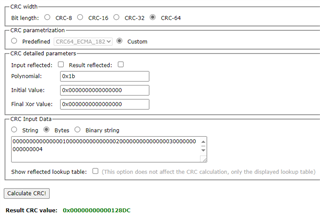

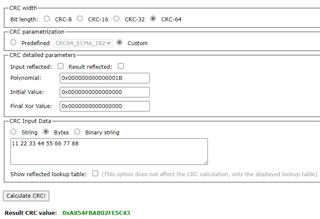

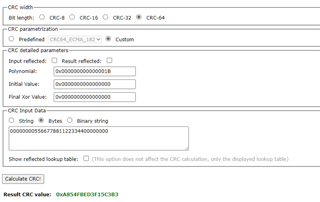

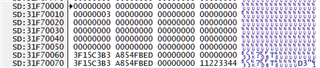

I get the same results as in online calculator only if I put eight '0' before the uint32 value (see picture).

For example If I have four "4 byte" values from 1 to 4, I get the checksum result of 0x00000000000128DC.