Other Parts Discussed in Thread: LMK5B33216

Hi,

i'm running a PTP stack which shifts the main 25 MHz clock to AM64 to achieve ToD alignment.

I have three devices leader (L), follower 1 (F1), and follower 2 (F2).

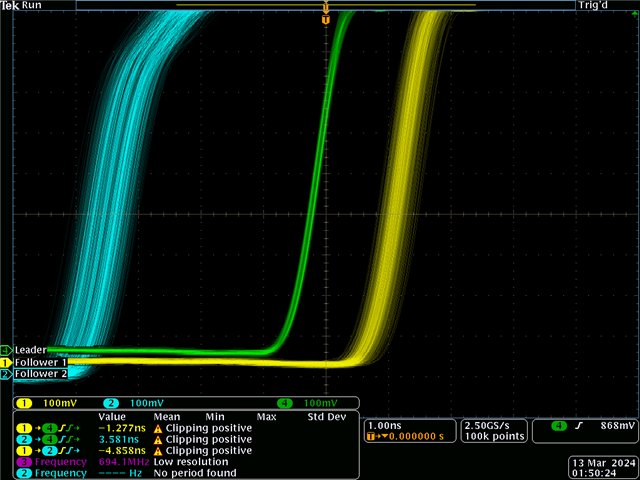

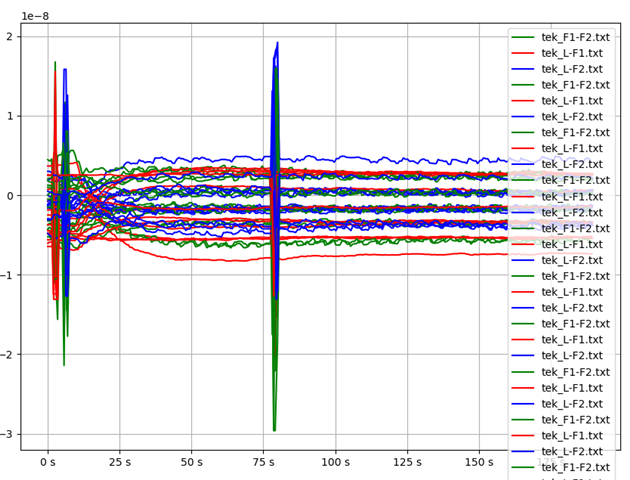

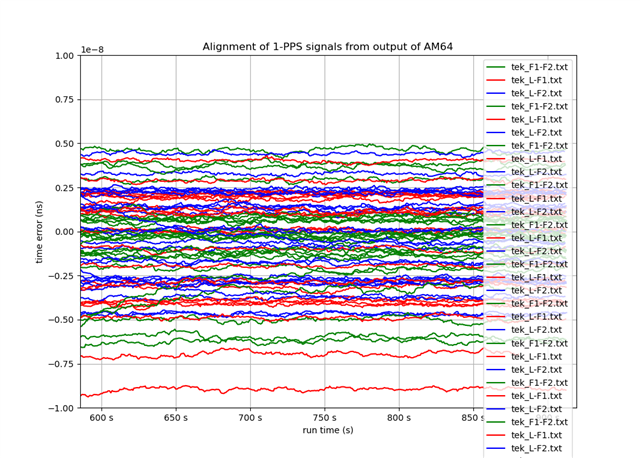

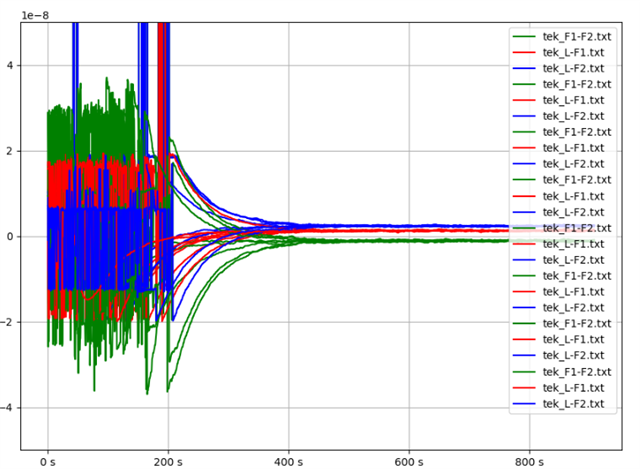

Below you can see a plot 1-PPS alignment from AM64 SK EVM from J3 with...

- green as follower time vs follower 2.

- red with leader vs. follower 1

- and blue with leader vs. follower 2.

For several runs in which I rebooted the system and restarted my PTP stack. The time error appears to be +5 ns to -10 ns on the alignment.

How can this be improved?

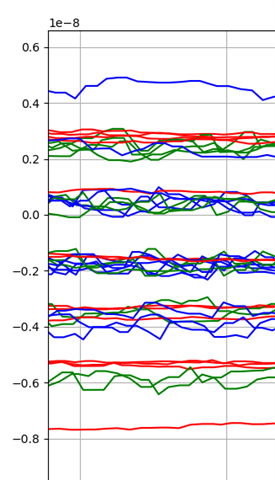

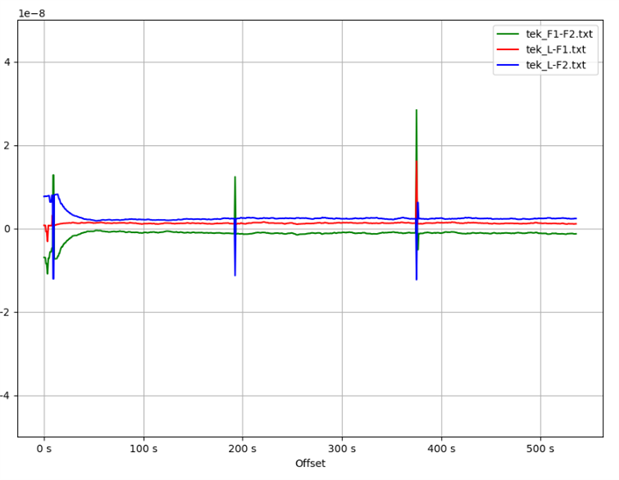

Here is a lessor set of data where I just start/stop my PTP stack. In this case alignment occurs deterministically, although I would like it to be all closer to 0.

I also did I a test where I turned the 1-PPS off/on... I must do this once to get 1-PPS to properly reflect the TOD. It seems there is no 'sample' error caused by this action. So why the non-determinism in my first plot?

testptp -i /dev/ptp0 -P 0

testptp -i /dev/ptp0 -P 1

Note, since my PTP stack is doing DCO of LMK5B33216 externally, I do not believe the bug discussed below impacts me... perhaps I'm wrong.

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1256953/sk-am62-pps-out-not-acting-as-expected

Which I found from:

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1248172/sk-am62-high-precission-pps-input

73,

Timothy