Other Parts Discussed in Thread: AM625, AM69

Hi

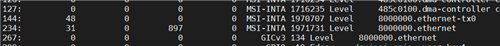

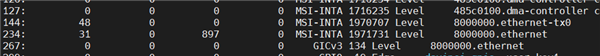

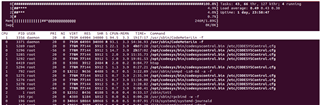

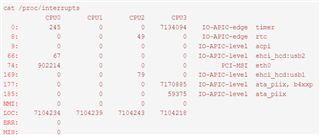

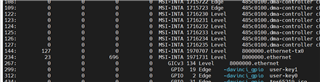

How can I know the specific ETH0 interrupt number。

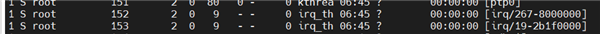

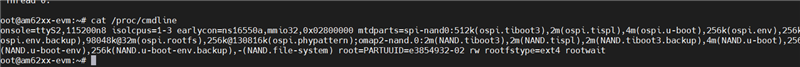

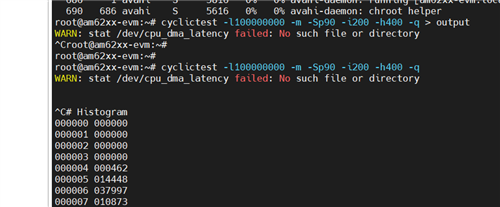

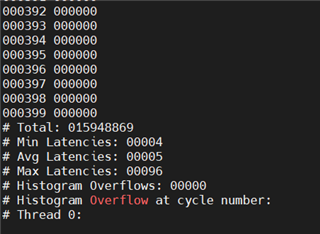

but in SDK8.6 linux is this

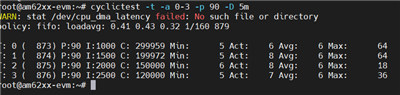

Because I'm using isolcpus to isolate the kernel, I want to rebind the network interrupt to a kernel, so I need to know where the network interrupt is.

Thanks