I'm trying to do a UART serial loopback through the AM625 PRU, however, it's not working as desired, even using the Texas examples. Basically, TX/RX doesn't work.

The version of Code Composer Studio is 12.6.0.00008

I'm using the firmware that comes directly from the Texas Intruments website: tisdk-default-image-am62xx-evm.wic. I didn't configure anything different in it, just using the default version.

Below is the code attached and a video of the unexpected situation. Thanks

The code is here:

#include <stdint.h>

#include <pru_uart.h>

#include "resource_table.h"

#define FIFO_SIZE 16

#define MAX_CHARS 8

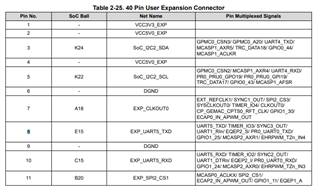

#define TX_PR0_UART_PINMUX ( *( volatile uint32_t * )( 0x000F41DC ) )

#define RX_PR0_UART_PINMUX ( *( volatile uint32_t * )( 0x000F41D8 ) )

void main(void)

{

uint8_t tx = 0;

volatile uint8_t rx = 0;

uint8_t cnt = 0;

volatile uint32_t status_0 = 0;

volatile uint32_t status_1 = 0;

char* hostBuffer;

volatile uint32_t map_0 = 0;

volatile uint32_t map_1 = 0;

// PINMUX configuration for UART_PRU TX/RX on 40 pins expansions header

TX_PR0_UART_PINMUX &=~ 0b111;

TX_PR0_UART_PINMUX |= 0b110;

map_0 = TX_PR0_UART_PINMUX;

RX_PR0_UART_PINMUX &=~ 0b111;

RX_PR0_UART_PINMUX |= 0b110;

map_1 = RX_PR0_UART_PINMUX;

// 115200 baud rate - 16x oversample - 192MHz clk

CT_UART.DIVLSB_bit.DLL = 104;

CT_UART.DIVMSB_bit.DLH = 0b0;

CT_UART.MODE_bit.OSM_SEL = 0b0;

// INTERRUPTS:

// Receiver Data Available Interrupt

// Transmitter Holding Register Empty Interrupt

// Line Status Interrupt

CT_UART.INT_EN_bit.ERBI = 0b1;

CT_UART.INT_EN_bit.ETBEI = 0b1;

CT_UART.INT_EN_bit.ELSI = 0b1;

// FIFO config

CT_UART.INT_FIFO_bit.FCR_FIFOEN = 0b1;

CT_UART.INT_FIFO_bit.FCR_RXCLR = 0b1;

CT_UART.INT_FIFO_bit.FCR_TXCLR = 0b1;

CT_UART.INT_FIFO_bit.FCR_DMAMODE1 = 0b1;

// 8-bit word, 1 stop bit, no parity, no break control and no divisor latch

CT_UART.LCTR_bit.WLS0 = 0b1;

CT_UART.LCTR_bit.WLS1 = 0b1;

// enable UART to act free and enable TX RX

CT_UART.PWR_bit.FREE = 0b1;

CT_UART.PWR_bit.URRST = 0b1;

CT_UART.PWR_bit.UTRST = 0b1;

// Enable LOOPBACK and disable AFE and RTS functionality

CT_UART.MCTR_bit.LOOP = 0b0;

CT_UART.MCTR_bit.AFE = 0b0;

CT_UART.MCTR_bit.RTS = 0b0;

hostBuffer = "abc";

while(1)

{

cnt = 0;

while(1)

{

//status verify

status_0 = CT_UART.LSR1;

status_1 = CT_UART.INT_FIFO;

if ((tx = hostBuffer[cnt]) == '\0') break;

cnt++;

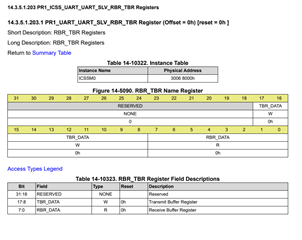

CT_UART.RBR_TBR_bit.TBR_DATA = tx;

//status verify

status_0 = CT_UART.LSR1;

status_1 = CT_UART.INT_FIFO;

while ( CT_UART.LSR1_bit.DR );

//status verify

status_0 = CT_UART.LSR1;

status_1 = CT_UART.INT_FIFO;

rx = CT_UART.RBR_TBR_bit.RBR_DATA;

//status verify

status_0 = CT_UART.LSR1;

status_1 = CT_UART.INT_FIFO;

while ( !CT_UART.LSR1_bit.TEMT );

}

}

// Disable UART before halting

CT_UART.PWR_bit.FREE = 0b0;

CT_UART.PWR_bit.URRST = 0b0;

CT_UART.PWR_bit.UTRST = 0b0;

// halt PRU core

__halt();

}

The video of the issue is here: