Part Number: AM625

Hi TI,

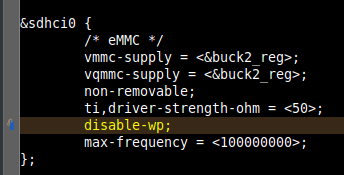

We use SDK: 09_01_00_08 , Kernel Version: 6.1.46-rt13 in our custom board.

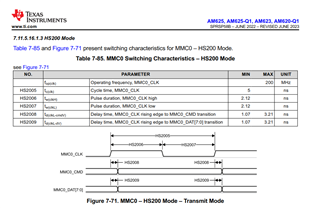

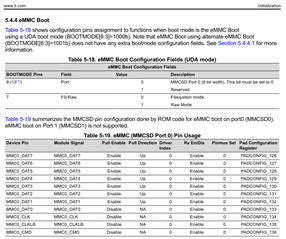

We use emmc sdhci0 on speed HS200 ,then to test Repeatedly power on and off.

1.

we found sometimes sdhci0 will happened error about in one hour ,detail log as Attached file.

sdhci-am654 fa10000.mmc: __mmc_blk_ioctl_cmd: cmd error -84

I/O error, dev mmcblk0, sector 25533296 op 0x0:(READ) flags 0x80700 phys_seg 32 prio class 2

2.

we found if change devices-tree sdhci0 max-frequency to 100M , run one day until now not happened this error.

but it case mmc HS200 read speed down to about 85~89MB/s.

could you fix this Error?