Other Parts Discussed in Thread: AM625

Dear TI team,

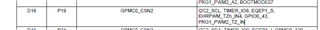

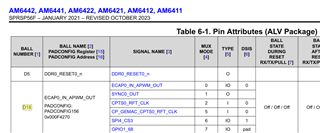

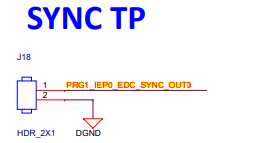

On our AM6442 we have a PTP synchronization over a switched Ethernet connection, where HSR or PRP will be running, so the PTP packets will come in one of the PRU subsystems. We want to generate a PPS signal based on this synchronization and mux it onto a pin, from which we will feed external PLLs.

- Which pin can I use?

- Is it the CPTS peripheral, which will handle the synchronization and the PPS generation?

- How do I have to change the device tree file? I tried something similar on an AM625, there the patch in the attachment worked, but I don't understand it. How do I do something similar on the AM6442? Note that on the AM625 we had PTP running over "normal" Ethernet, here we have it running over a PRU subsystem (probably on HSR).

Kind regards,

Leon

diff --git a/arch/arm64/boot/dts/ti/k3-am625-sk.dts b/arch/arm64/boot/dts/ti/k3-am625-sk.dts

index 83525949aafd..f27cac1fac02 100644

--- a/arch/arm64/boot/dts/ti/k3-am625-sk.dts

+++ b/arch/arm64/boot/dts/ti/k3-am625-sk.dts

@@ -147,6 +147,7 @@ AM62X_IOPAD(0x174, PIN_OUTPUT, 0) /* (AD21) RGMII2_TD2 */

AM62X_IOPAD(0x178, PIN_OUTPUT, 0) /* (AC20) RGMII2_TD3 */

AM62X_IOPAD(0x168, PIN_OUTPUT, 0) /* (AE21) RGMII2_TXC */

AM62X_IOPAD(0x164, PIN_OUTPUT, 0) /* (AA19) RGMII2_TX_CTL */

+ AM62X_IOPAD(0x1F0, PIN_OUTPUT, 1) /* (A18) EXT_REFCLK1.SYNC1_OUT Leon: added here for test */

>;

};

@@ -371,6 +372,8 @@ cpsw_cpts: cpsw-cpts {

pinctrl-single,pins = <

/* pps [cpsw cpts genf1] in17 -> out12 [cpsw cpts hw3_push] */

K3_TS_OFFSET(12, 17)

+ /* pps [cpsw cpts genf1] in17 -> out21 [cpsw cpts SYNC1_OUT] */

+ K3_TS_OFFSET(21, 17)

>;

};

};