Hi,

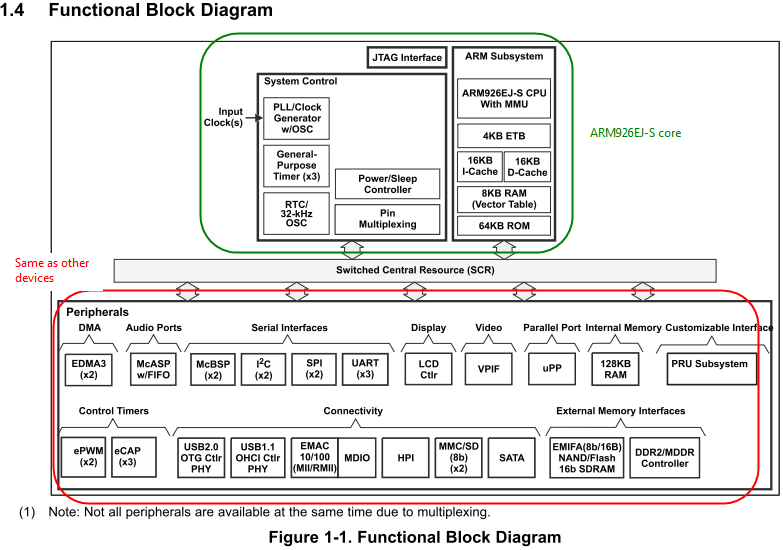

I would like to ask a question on AM18x processors. The attached diagram is from SPRS653A, AM1808 ARM Microprocessor.

I have compared Peripherals (I2C, EDMA, MSASP, LCDc, VPIF) feature and usage with other TI devices not in the ARM family (OMAP, DaVinci, MPU) and found that these peripherals are almost the same. This means that AM18x and AM18x uses the same peripheral design as other devices.

On the other hand, AM18x uses ARM926EJ-S RISC core, which is different from devices that I compared with above. So schematically, does AM18x consisting of two parts:

1. Core: ARM926EJ-S

2. Peripherals: same as other TI devices

?

Is this understanding correct?

And for the part I enclosed in green circle, is it 100% prescribed in ARM926EJ-S standard? It makes sense that the instruction set must be fully ARM926EJ-S compatible, but does TI add instruction set extension to that? Does ARM allowed licensed manufacturers to add their own instruction extensions?

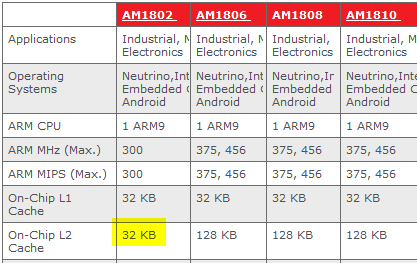

And regarding L1, L2 cache and memory size, is it fully specified in ARM standards? Does ARM allow manufacturer to determine it themselves? It seems to me reasonable, and I have found that AM1802 has less L2 cache than other devices which is a counterexample if on-chip memory/cache sizes are fully prescribed by ARM; or does ARM prescribe a range (like 32KB~256KB) in this case?

I am new to ARM. Hope someone could explain these questions.

Zheng