Other Parts Discussed in Thread: TDA4VH, SYSCONFIG

My SDK version:

linux: ti-processor-sdk-linux-adas-j784s4-evm-09_01_00_06

rtos: ti-processor-sdk-rtos-j784s4-evm-09_01_00_06

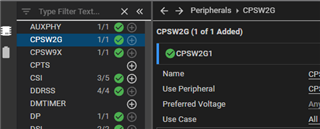

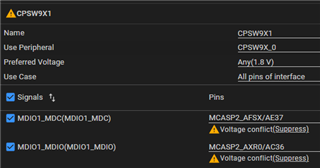

The CPSW2G pin in the native SDK package is connected to the RTL9000AA_RTL9000AN Ethernet device,

and the CPSW2G pin in our test board is directly connected to the external switch chip,

may I ask how to modify the driver to make the Ethernet connected?

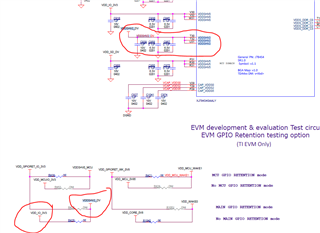

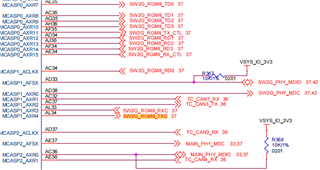

The following is a partial hardware schematic of our test board:

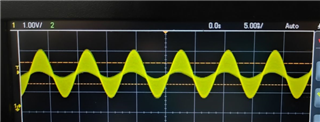

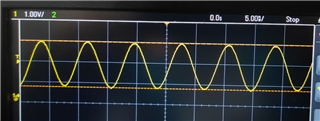

j784s4 side:

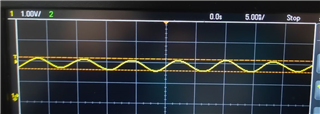

switch chip(BCM89571) side:

Above, thank you.