Other Parts Discussed in Thread: TMDS64EVM, SYSCONFIG

Hi,

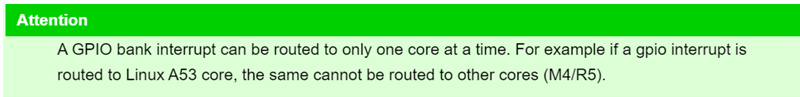

is it possible to share the gpio interrupt of the main gpio interface?

I've seen the documentation:

AM64x MCU+ SDK: GPIO Input Interrupt

And also the forum entry:

It is somehow possible the share the interrupt between A53 (linux) and R5F?

BR

Artur