Part Number: AM6411

We need to interface a chip with a proprietary 32 bit parallel interface. It works a lot like an SPI with 32 data lines. 100MHz clock frequence would be great but 50MHz is good enough/acceptable. We are considering AM6411 for this purpose.

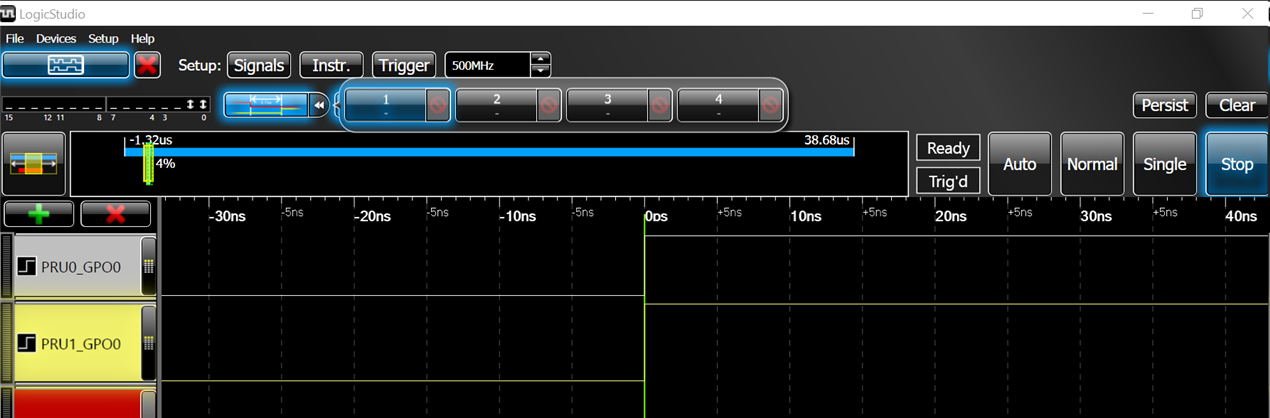

However, I noticed in datasheet each PRU unit has only 20 output pins. Can I gang pru0 and pru1 together to implement a 32bit data bus? We only need output mode. Hopefully there is a hardware-based mechanism to reduce the synchronization overhead. If several clocks are required to sync two PRU units, I am worried that the actual data clock would drop too low.

Any confirmation and data rate estimation would be appreciated.