Hi, I am using C665x DSP to develop a data communication software.

The development environment is as follows:

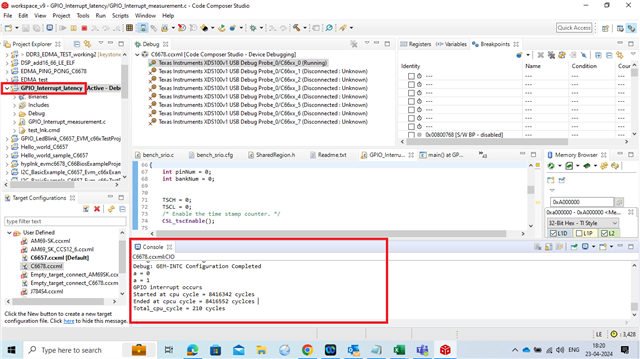

1. Device: TMS320C6657, run clock = 800MHz;

2.CCS V5.5;

3.No real-time OS is used;

4. Only One GPIO Interrupt is used, and the interrupt signal is generated externally, period = 6.4uS;

5. Software is running in internal ram;

I measured the time from GPIO Interrupt Signal to enter Interrupt Service routine, it changes greatly,

and the maximum time is about 2.0uS(1600 cycles).

Is there a method to shorten this time?