Hi expert,

In the spec of eMMC, it is required that the minimum data hold time should be 0.8ns. But in the actual measurement, customer find the hold time of the most data lines cannot meet this requirement. So customers would like to know if we can adjust some parameters/registers to make the timing in the spec? Thanks

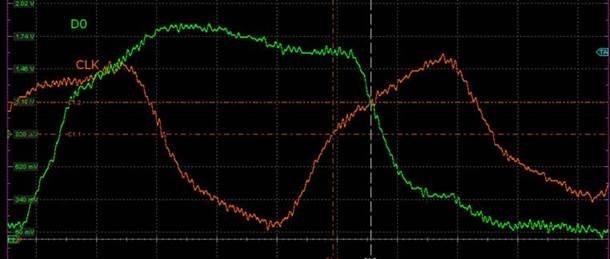

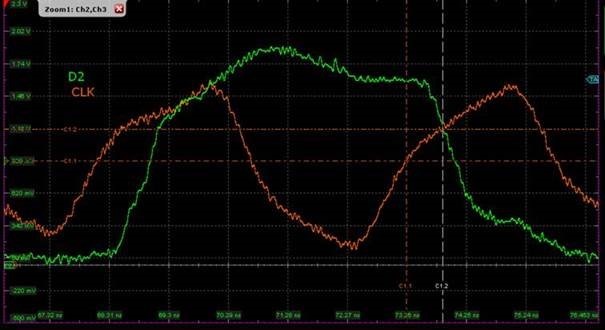

DAT[0]:0.5963ns

DAT[1]:0.6972ns

DAT[2]:0.6039ns

DAT[3]: 0.519ns

DAT[4]: 0.85ns

DAT[5]: 0.8448ns

DAT[6]: 0.627ns

DAT[7]: 0.752ns

Best Regards,

Xingyu Zhu