Part Number: TDA4VM

Hello together,

we are trying to test the DSI output on the TDA4VM processor, unfortunately at some resolutions we don't see any output signal, for example at 1280x720. Could you please advise us which parameter is necessary to change?

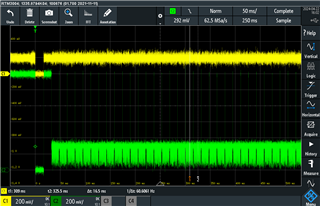

TVG generator is working without any issue. DSI signal is stable in that case.

But when we try to use DPI output from DSS as the source of signal for DSI data line stays in IDLE state.

Continuous clock is stable at correct frequency.

We have tested several other DSI ref. clock frequencies without success.

Then we have tried several other resolutions and some of them are working and some not.

No error was detected by the driver. We are not found any rule what is behind that, just

some resolutions are working while other not. (examples are at the end of this report)

Workaround:

We have applied the patch for exact clock setting - drivers/clk/keystone/sci-clk.c

We have applied the patch "Wait time for Calibrations enable after bandgap is enabled" - drivers/phy/cadence/cdns-dphy.c

We have updated drivers/phy/cadence/cdns-dphy.c driver to allow set arbitrary reference clock using as source

the output from main PLL_3 HSDIVOUT4. Also we have tested that with fixed ref-clk 19.2Mhz and 24Mhz

-------------------------------------------------------------------------------------------------------------------------------------

*************************************************************************************************************************************

-------------------------------------------------------------------------------------------------------------------------------------

Mode definition:

&lvdspanel {

panel-timing {

clock-frequency = <74250000>;

hactive = <1280>;

vactive = <720>;

hsync-len = <40>;

hfront-porch = <262>;

hback-porch = <70>;

vsync-len = <5>;

vfront-porch = <5>;

vback-porch = <20>;

};

};

-------------------------------------------------------------------------------------------------------------------------------------

DSS and DSI setting:

&dphy2 {

status = "okay";

#ifdef DSI_ON_MAIN3_HSDIV4

/delete-property/ assigned-clocks;

/delete-property/ assigned-clock-parents;

/delete-property/ assigned-clock-rates;

assigned-clocks = <&k3_clks 296 3>;

assigned-clock-parents = <&k3_clks 296 6>;

assigned-clock-rates = <19200000>;

#else

/delete-property/ assigned-clock-rates;

assigned-clock-rates = <24000000>; // sysclk OSC

#endif

};

&dsi0 {

status = "okay";

};

&dss {

status = "okay";

/*

* These clock assignments are chosen to enable the following outputs:

*

* VP0 - DisplayPort SST

* VP1 - DPI0

* VP2 - DSI

* VP3 - DPI1

*/

assigned-clocks = <&k3_clks 152 1>,

<&k3_clks 152 4>,

<&k3_clks 152 9>,

<&k3_clks 152 13>;

assigned-clock-parents = <&k3_clks 152 2>, /* PLL16_HSDIV0 */

<&k3_clks 152 6>, /* PLL19_HSDIV0 */

<&k3_clks 152 11>, /* PLL18_HSDIV0 */

<&k3_clks 152 18>; /* PLL23_HSDIV0 */

};

&dss_ports {

.....

};

&dsi0_ports {

.....

};

-------------------------------------------------------------------------------------------------------------------------------------

*************************************************************************************************************************************

-------------------------------------------------------------------------------------------------------------------------------------

HW State:

we have checked the state of hardware by reading registers but

only reported hardware status is:

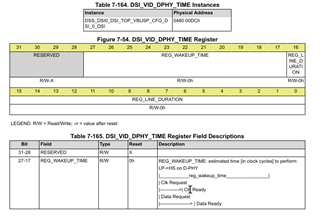

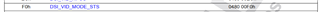

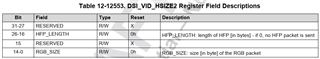

DSI_VID_MODE_STS_FLAG:

root@j721e-cgtst4m:~# devmem2 0x4800180

/dev/mem opened.

Memory mapped at address 0xffff93c84000.

Read at address 0x04800180 (0xffff93c84180): 0x00000005

bits ERR_MISSING_HSYNC_FLAG and VSG_STS_FLAG are set

It looks that there is some effort to fill DSI FIFO

DSI_DPI_CFG:

root@j721e-cgtst4m:~# devmem2 0x48001ac

/dev/mem opened.

Memory mapped at address 0xffffb9048000.

Read at address 0x048001AC (0xffffb90481ac): 0x08000004

root@j721e-cgtst4m:~# devmem2 0x48001ac

/dev/mem opened.

Memory mapped at address 0xffff80cbb000.

Read at address 0x048001AC (0xffff80cbb1ac): 0x08000003

bit DPI_CFG_FIFO_LEVEL changes but values are from 0 up to 8

-------------------------------------------------------------------------------------------------------------------------------------

*************************************************************************************************************************************

-------------------------------------------------------------------------------------------------------------------------------------

DRIVER LOG:

Driver log was enhanced to see current setting:

DSI size parameters:

[ 6.861946] cdns-dsi 4800000.dsi: cdns_dsi_bridge_enable: HFP = 780

[ 6.861951] cdns-dsi 4800000.dsi: cdns_dsi_bridge_enable: HSA = 106

[ 6.861955] cdns-dsi 4800000.dsi: cdns_dsi_bridge_enable: HBP = 198

[ 6.861959] cdns-dsi 4800000.dsi: cdns_dsi_bridge_enable: HACT = 3840

[ 6.861964] cdns-dsi 4800000.dsi: cdns_dsi_bridge_enable: HTOTAL = 4956

[ 6.861968] cdns-dsi 4800000.dsi: cdns_dsi_bridge_enable: VFP = 5

[ 6.861972] cdns-dsi 4800000.dsi: cdns_dsi_bridge_enable: VSA = 6

[ 6.861976] cdns-dsi 4800000.dsi: cdns_dsi_bridge_enable: VBP = 19

[ 6.861980] cdns-dsi 4800000.dsi: cdns_dsi_bridge_enable: VACT = 720

-------------------------------------------------------------------------------------------------------------------------------------

DPHY PLL setting:

[ 8.886544] phy phy-4480000.phy.14: cdns_dphy_config_from_opts: Phy Config VALID

[ 8.886550] phy phy-4480000.phy.14: cdns_dsi_get_dphy_pll_cfg: ref clk is - 44550000

[ 8.886574] phy phy-4480000.phy.14: cdns_dsi_get_dphy_pll_cfg: hs clk is - 445500000

[ 8.886579] phy phy-4480000.phy.14: cdns_dsi_get_dphy_pll_cfg: PLL SETUP:

[ 8.886583] phy phy-4480000.phy.14: cdns_dsi_get_dphy_pll_cfg: ipdiv = 4

[ 8.886587] phy phy-4480000.phy.14: cdns_dsi_get_dphy_pll_cfg: opdiv = 4

[ 8.886592] phy phy-4480000.phy.14: cdns_dsi_get_dphy_pll_cfg: fbdiv = 320

-------------------------------------------------------------------------------------------------------------------------------------

*************************************************************************************************************************************

-------------------------------------------------------------------------------------------------------------------------------------

System PLL settings:

-------------------------------------------------------------------------------------------------------------------------------------

DPHY:

it is connected to <296 6> => DEV_DPHY_TX0_DPHY_REF_CLK_PARENT_HSDIV4_16FFT_MAIN_3_HSDIVOUT4_CLK

root@j721e-cgtst4m:~# k3conf dump clock 296

|------------------------------------------------------------------------------|

| VERSION INFO |

|------------------------------------------------------------------------------|

| K3CONF | (version 0.3-nogit built Fri Oct 06 12:20:16 UTC 2023) |

| SoC | J721E SR1.1 |

| SYSFW | ABI: 3.1 (firmware version 0x0009 '9.1.2--v09.01.02 (Kool Koala))') |

|------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------|

| Device ID | Clock ID | Clock Name | Status | Clock Frequency |

|-------------------------------------------------------------------------------------------------------------------------------|

| 296 | 0 | DEV_DPHY_TX0_CLK | CLK_STATE_READY | 125000000 |

| 296 | 1 | DEV_DPHY_TX0_PSM_CLK | CLK_STATE_READY | 20000000 |

| 296 | 2 | DEV_DPHY_TX0_IP1_PPI_M_TXCLKESC_CLK | CLK_STATE_READY | 20000000 |

| 296 | 3 | DEV_DPHY_TX0_DPHY_REF_CLK | CLK_STATE_READY | 44550000 |

| 296 | 4 | DEV_DPHY_TX0_DPHY_REF_CLK_PARENT_GLUELOGIC_HFOSC0_CLKOUT | CLK_STATE_READY | 24000000 |

| 296 | 5 | DEV_DPHY_TX0_DPHY_REF_CLK_PARENT_BOARD_0_HFOSC1_CLK_OUT | CLK_STATE_READY | 0 |

| 296 | 6 | DEV_DPHY_TX0_DPHY_REF_CLK_PARENT_HSDIV4_16FFT_MAIN_3_HSDIVOUT4_CLK | CLK_STATE_READY | 44550000 |

| 296 | 7 | DEV_DPHY_TX0_DPHY_REF_CLK_PARENT_HSDIV4_16FFT_MAIN_2_HSDIVOUT4_CLK | CLK_STATE_READY | 100000000 |

| 296 | 8 | DEV_DPHY_TX0_IP1_PPI_TXBYTECLKHS_CL_CLK | CLK_STATE_READY | 0 |

| 296 | 9 | DEV_DPHY_TX0_IP1_PPI_M_RXCLKESC_CLK | CLK_STATE_READY | 0 |

| 296 | 10 | DEV_DPHY_TX0_CK_P | CLK_STATE_READY | 0 |

| 296 | 11 | DEV_DPHY_TX0_CK_M | CLK_STATE_READY | 0 |

| 296 | 12 | DEV_DPHY_TX0_IP2_PPI_TXBYTECLKHS_CL_CLK | CLK_STATE_READY | 0 |

|-------------------------------------------------------------------------------------------------------------------------------|

-------------------------------------------------------------------------------------------------------------------------------------

DSI core

root@j721e-cgtst4m:~# k3conf dump clock 150

|------------------------------------------------------------------------------|

| VERSION INFO |

|------------------------------------------------------------------------------|

| K3CONF | (version 0.3-nogit built Fri Oct 06 12:20:16 UTC 2023) |

| SoC | J721E SR1.1 |

| SYSFW | ABI: 3.1 (firmware version 0x0009 '9.1.2--v09.01.02 (Kool Koala))') |

|------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------|

| Device ID | Clock ID | Clock Name | Status | Clock Frequency |

|--------------------------------------------------------------------------------------------------|

| 150 | 0 | DEV_DSS_DSI0_DPHY_0_RX_ESC_CLK | CLK_STATE_READY | 0 |

| 150 | 1 | DEV_DSS_DSI0_DPI_0_CLK | CLK_STATE_READY | 0 |

| 150 | 2 | DEV_DSS_DSI0_PLL_CTRL_CLK | CLK_STATE_READY | 500000000 |

| 150 | 3 | DEV_DSS_DSI0_PPI_0_TXBYTECLKHS_CL_CLK | CLK_STATE_READY | 0 |

| 150 | 4 | DEV_DSS_DSI0_DPHY_0_TX_ESC_CLK | CLK_STATE_READY | 20000000 |

| 150 | 5 | DEV_DSS_DSI0_SYS_CLK | CLK_STATE_READY | 250000000 |

|--------------------------------------------------------------------------------------------------|

-------------------------------------------------------------------------------------------------------------------------------------

TIDSS

root@j721e-cgtst4m:~# k3conf dump clock 152

|------------------------------------------------------------------------------|

| VERSION INFO |

|------------------------------------------------------------------------------|

| K3CONF | (version 0.3-nogit built Fri Oct 06 12:20:16 UTC 2023) |

| SoC | J721E SR1.1 |

| SYSFW | ABI: 3.1 (firmware version 0x0009 '9.1.2--v09.01.02 (Kool Koala))') |

|------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Device ID | Clock ID | Clock Name | Status | Clock Frequency |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| 152 | 0 | DEV_DSS0_DSS_FUNC_CLK | CLK_STATE_READY | 600000000 |

| 152 | 1 | DEV_DSS0_DSS_INST0_DPI_0_IN_2X_CLK | CLK_STATE_READY | 600000000 |

| 152 | 2 | DEV_DSS0_DSS_INST0_DPI_0_IN_2X_CLK_PARENT_HSDIV1_16FFT_MAIN_16_HSDIVOUT0_CLK | CLK_STATE_READY | 600000000 |

| 152 | 3 | DEV_DSS0_DSS_INST0_DPI_0_IN_2X_CLK_PARENT_DPI_1_PCLK_SEL_OUT0 | CLK_STATE_READY | 600000000 |

| 152 | 4 | DEV_DSS0_DSS_INST0_DPI_1_IN_2X_CLK | CLK_STATE_READY | 600000000 |

| 152 | 5 | DEV_DSS0_DSS_INST0_DPI_1_IN_2X_CLK_PARENT_HSDIV1_16FFT_MAIN_17_HSDIVOUT0_CLK | CLK_STATE_READY | 600000000 |

| 152 | 6 | DEV_DSS0_DSS_INST0_DPI_1_IN_2X_CLK_PARENT_DPI0_EXT_CLKSEL_OUT0 | CLK_STATE_READY | 600000000 |

| 152 | 7 | DEV_DSS0_DSS_INST0_DPI_1_IN_2X_CLK_PARENT_DPI1_EXT_CLKSEL_OUT0 | CLK_STATE_READY | 600000000 |

| 152 | 8 | DEV_DSS0_DSS_INST0_DPI_1_IN_2X_CLK_PARENT_HSDIV1_16FFT_MAIN_16_HSDIVOUT0_CLK | CLK_STATE_READY | 600000000 |

| 152 | 9 | DEV_DSS0_DSS_INST0_DPI_2_IN_2X_CLK | CLK_STATE_READY | 74250000 |

| 152 | 10 | DEV_DSS0_DSS_INST0_DPI_2_IN_2X_CLK_PARENT_HSDIV1_16FFT_MAIN_16_HSDIVOUT0_CLK | CLK_STATE_READY | 600000000 |

| 152 | 11 | DEV_DSS0_DSS_INST0_DPI_2_IN_2X_CLK_PARENT_HSDIV1_16FFT_MAIN_18_HSDIVOUT0_CLK | CLK_STATE_READY | 74250000 |

| 152 | 12 | DEV_DSS0_DSS_INST0_DPI_2_IN_2X_CLK_PARENT_DPI0_EXT_CLKSEL_OUT0 | CLK_STATE_READY | 600000000 |

| 152 | 13 | DEV_DSS0_DSS_INST0_DPI_3_IN_2X_CLK | CLK_STATE_READY | 600000000 |

| 152 | 14 | DEV_DSS0_DSS_INST0_DPI_3_IN_2X_CLK_PARENT_HSDIV1_16FFT_MAIN_16_HSDIVOUT1_CLK | CLK_STATE_READY | 600000000 |

| 152 | 15 | DEV_DSS0_DSS_INST0_DPI_3_IN_2X_CLK_PARENT_HSDIV1_16FFT_MAIN_17_HSDIVOUT1_CLK | CLK_STATE_READY | 600000000 |

| 152 | 16 | DEV_DSS0_DSS_INST0_DPI_3_IN_2X_CLK_PARENT_HSDIV1_16FFT_MAIN_18_HSDIVOUT1_CLK | CLK_STATE_READY | 1188000000 |

| 152 | 17 | DEV_DSS0_DSS_INST0_DPI_3_IN_2X_CLK_PARENT_DPI0_EXT_CLKSEL_OUT0 | CLK_STATE_READY | 600000000 |

| 152 | 18 | DEV_DSS0_DSS_INST0_DPI_3_IN_2X_CLK_PARENT_DPI1_EXT_CLKSEL_OUT0 | CLK_STATE_READY | 600000000 |

| 152 | 23 | DEV_DSS0_DSS_INST0_DPI_0_OUT_CLK | CLK_STATE_READY | 0 |

| 152 | 24 | DEV_DSS0_DSS_INST0_DPI_0_OUT_2X_CLK | CLK_STATE_READY | 0 |

| 152 | 25 | DEV_DSS0_DSS_INST0_DPI_1_OUT_CLK | CLK_STATE_READY | 0 |

| 152 | 27 | DEV_DSS0_DSS_INST0_DPI_2_OUT_CLK | CLK_STATE_READY | 0 |

| 152 | 29 | DEV_DSS0_DSS_INST0_DPI_3_OUT_CLK | CLK_STATE_READY | 0 |

| 152 | 31 | DEV_DSS0_DPI0_EXT_CLKSEL | CLK_STATE_READY | 600000000 |

| 152 | 32 | DEV_DSS0_DPI0_EXT_CLKSEL_PARENT_HSDIV1_16FFT_MAIN_19_HSDIVOUT0_CLK | CLK_STATE_READY | 600000000 |

| 152 | 33 | DEV_DSS0_DPI0_EXT_CLKSEL_PARENT_BOARD_0_VOUT1_EXTPCLKIN_OUT | CLK_STATE_READY | 0 |

| 152 | 34 | DEV_DSS0_DPI1_EXT_CLKSEL | CLK_STATE_READY | 600000000 |

| 152 | 35 | DEV_DSS0_DPI1_EXT_CLKSEL_PARENT_HSDIV1_16FFT_MAIN_23_HSDIVOUT0_CLK | CLK_STATE_READY | 600000000 |

| 152 | 36 | DEV_DSS0_DPI1_EXT_CLKSEL_PARENT_BOARD_0_VOUT2_EXTPCLKIN_OUT | CLK_STATE_READY | 0 |

|-----------------------------------------------------------------------------------------------------------------------------------------|

-------------------------------------------------------------------------------------------------------------------------------------

*************************************************************************************************************************************

-------------------------------------------------------------------------------------------------------------------------------------

LIST of tested modes:

// DSI: htotal=2880, crtc_htotal=960, hs_clk=171,414Mhz hs_byte_clk=21.5Mhz,

// DSI: Dynamic REFCLK=12.2Mhz, idiv=2 ,odiv=8 ,fbdiv=286 fcalc= 171.600Mhz: OK;

// DSI: Static REFCLK=19.2Mhz, idiv=2 ,odiv=8 ,fbdiv=286 fcalc= 171.600Mhz: OK;

// DSI: Static REFCLK=24Mhz, idiv=2 ,odiv=8 ,fbdiv=229 fcalc= 171.750Mhz: OK;

&lvdspanel {

panel-timing {

clock-frequency = <28569600>;

hactive = <800>;

vactive = <480>;

hsync-len = <32>;

hfront-porch = <48>;

hback-porch = <80>;

vsync-len = <7>;

vfront-porch = <3>;

vback-porch = <6>;

};

};

// DSI: htotal=3168, crtc_htotal=1056, hs_clk=240Mhz hs_byte_clk=30Mhz,

// DSI: DPI(HFP) > DSI(HSS+HSA+HSE+HBP) :: 38400000000 == 25920000000

// DSI: Dynamic REFCLK=24Mhz: idiv=2,odiv=8,fbdiv=320 fcalc=240Mhz: Not working, TVG OK;

// DSI: Static REFCLK=19.2Mhz, idiv=2,odiv=8,fbdiv=400 fcalc=240Mhz: Not working; TVG not tested;

// DSI: Static REFCLK=24Mhz, idiv=2,odiv=8,fbdiv=320 fcalc=240Mhz: Not working; TVG OK;

&lvdspanel {

panel-timing {

clock-frequency = <40000000>;

hactive = <800>;

vactive = <600>;

hsync-len = <128>;

hfront-porch = <40>;

hback-porch = <88>;

vsync-len = <4>;

vfront-porch = <1>;

vback-porch = <23>;

};

};

// DSI: htotal=3840, crtc_htotal=1280, hs_clk=390Mhz hs_byte_clk=48.75Mhz,

// DSI: DPI(HFP) > DSI(HSS+HSA+HSE+HBP) :: 62400000000 == 42120000000

// DSI: Dynamic REFCLK=39Mhz: idiv=4 ,odiv=4 ,fbdiv=320 fcalc=390Mhz: OK;

// DSI: Static REFCLK=19.2Mhz, idiv=2 ,odiv=4 ,fbdiv=325 fcalc=390Mhz: OK;

// DSI: Static REFCLK=24Mhz, idiv=2 ,odiv=4 ,fbdiv=260 fcalc=390Mhz: OK;

&lvdspanel {

panel-timing {

clock-frequency = <65000000>;

hactive = <1024>;

vactive = <768>;

hsync-len = <136>;

hfront-porch = <40>;

hback-porch = <80>;

vsync-len = <6>;

vfront-porch = <3>;

vback-porch = <29>;

};

};

// DSI: htotal=4320, crtc_htotal=1440 hs_clk=445,5Mhz hs_byte_clk=55.6875Mhz,

// DSI: Dynamic REFCLK=44.55Mhz: idiv=4,odiv=4,fbdiv=320 fcalc=445.5Mhz: Not working, TVG OK;

// DSI: Static REFCLK=19.2Mhz, idiv=2,odiv=4,fbdiv=372 fcalc=446.4Mhz: Not working; TVG OK;

&lvdspanel {

panel-timing {

clock-frequency = <74250000>;

hactive = <1280>;

vactive = <720>;

hsync-len = <40>;

hfront-porch = <112>; // originaly <110>

hback-porch = <220>;

vsync-len = <5>;

vfront-porch = <5>;

vback-porch = <20>;

};

};

// DSI: htotal=4320, crtc_htotal=1440, hs_clk=413.4Mhz hs_byte_clk=51.675Mhz, main18/hsdiv1=1584700000

// DSI: Dynamic REFCLK=41,34Mhz: idiv=4,odiv=4,fbdiv=320 fcalc=413.4Mhz: OK;

// DSI: Static REFCLK=19.2Mhz, idiv=2,odiv=4,fbdiv=345 fcalc=413.4Mhz: OK - some shifts at LVDS side, not problem of DSI;

// DSI: Static REFCLK=24Mhz, idiv=2,odiv=4,fbdiv=276 fcalc=413.4Mhz: OK - some shifts at LVDS side;

&lvdspanel {

panel-timing {

clock-frequency = <68900000>;

hactive = <1280>;

vactive = <800>;

hsync-len = <80>;

hfront-porch = <40>;

hback-porch = <40>;

vsync-len = <10>;

vfront-porch = <3>;

vback-porch = <10>;

};

};

// DSI: htotal=5400, crtc_htotal=1800, hs_clk=515.196Mhz hs_byte_clk=64.3995Mhz, main18/hsdiv1=1545588000

// DSI: Dynamic REFCLK=51,5196Mhz: idiv=4 ,odiv=4 ,fbdiv=320 fcalc= 515.196Mhz: OK;

&lvdspanel {

panel-timing {

clock-frequency = <85866392>;

hactive = <1368>;

vactive = <768>;

hsync-len = <144>;

hfront-porch = <72>;

hback-porch = <216>;

vsync-len = <3>;

vfront-porch = <1>;

vback-porch = <23>;

};

};

Kind regards,

David

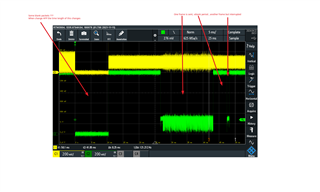

. First I see the transition from idle to HS for some time period (the length of that time period changes when I update HFP and BlkLinePulse). Then I see one frame sent. During VBLANK the data line is in iddle state. Then another frame started but after blanking the data line is stopped to the idle. Mising HSYNC is then reported as the error.

. First I see the transition from idle to HS for some time period (the length of that time period changes when I update HFP and BlkLinePulse). Then I see one frame sent. During VBLANK the data line is in iddle state. Then another frame started but after blanking the data line is stopped to the idle. Mising HSYNC is then reported as the error.