Other Parts Discussed in Thread: AM6442, SYSCONFIG

Hello TI support team.

I have a question about EVM's Enet Layer 2 CPSW Example.

The SDK is mcu_plus_sdk_am64x_08_06_00_45.

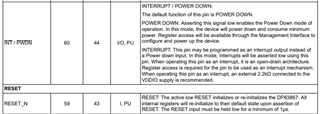

Please tell me about INT/PWDN and RESET_N of CPSW RGMII1-PHY (DP83867).

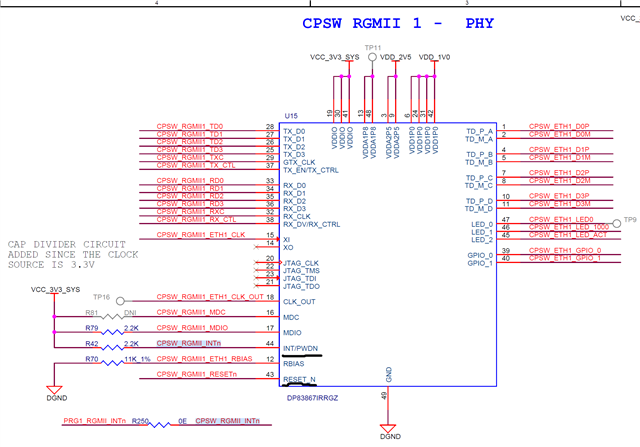

In EVM, the PHY is connected to AM6442 as shown below.

・INT/PWDN - CPSW_RGMII_INTn - PRG1_RGMII_INTn - PRG1_RGMII_INTn_RC - EXT_INTN(C19 @AM6442)

・RESET_N - CPSW_RGMII1_RESETn - GPIO_CPSW1_RST (IO EXPANDER)

Where are these ports configured in the cpsw source code?

Also where are these ports used in the source code?

It was not in the sysconfig settings from CCS. Please let me know.

Best regards,

Kiyomasa Imaizumi.