Hi, Expert

Customer want to achieve this flow, please help to evaluate feasibility, Thanks.

GPIO as interrupt trigger

GPIO falling edge, interrupt routed to DMA

DMA access NAND via GPMC, move data from NAND to other memory.

Regards

Zekun

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi, Expert

Customer want to achieve this flow, please help to evaluate feasibility, Thanks.

GPIO as interrupt trigger

GPIO falling edge, interrupt routed to DMA

DMA access NAND via GPMC, move data from NAND to other memory.

Regards

Zekun

Yes, Tushar

I know it is systemic design. Please help to search.

Regards

Zekun

Hello Zekun,

Sorry for delayed reply , you may expect a reply by EOD.

Regards,

Anil.

I found that there are 10 GPIO can be routed to DMASS in main domain.

Hello Zekun,

Yes, it is possible with the help of GPIO we can trigger DMA other than NAND memories .

So, your GPIO input is the local event that even needs to be converted to a global event to transfer DMA.

Please look at the images below for more details.

Also in the GPMC module, I found there is also DMASS can be accessed.

Actually, GPMC_SDMAREQ is a local event. It is generated from the GPMC FIFO. When the GPMC FIFO is filled with 64bytes, then this event is triggered and based on this event ,GPMC can trigger DMA transferring data either source to destination memory or vice versa .

So, when GPMC is used the DMA , then this event is needed.

Now, you want to transfer data from NAND memory to destination memory with the help of GPIO.

This is not possible as there is already a local event (GPMC_SDMAREQ) and it is used by GPMC with DMA to transfer data from NAND memory to destination memory or vice versa. So, again, we can't add one more GPIO event to trigger the DMA event.

Now, How can you do?

Configure GPIO interrupt .

When the GPIO interrupt comes , call the DMA start API in the IRQ routine. This is the only way you can do it.

Regards,

Anil.

Hi Anil,

thanks for your reply, I just want to make sure, if I config GPMC to not to access a NAND/Nor memory but 'Asynchronous SRAM' , which is actually FPGA interface in our usage senario, would that have a different answer?

Because as I know, bus master can access this 'Asynchronous SRAM' simply by a memory mapped address.

"Asynchronous SRAM-like memories and application-specific integrated circuit (ASIC) devices" from AM64x-TRM

Also, here's a similar senario and discussion here, and ''Reply' said we can use GPIO to trigger the DMA channel between GPMC and DDR.

thanks for your reply, I just want to make sure, if I config GPMC to not to access a NAND/Nor memory but 'Asynchronous SRAM' , which is actually FPGA interface in our usage senario, would that have a different answer?

Because as I know, bus master can access this 'Asynchronous SRAM' simply by a memory mapped address.

Hello Jenny,

Your understanding is correct if you configure to PSRAM memory or NOR memory type, then we can trigger DMA based on GPIO input.

How to trigger DMA based on the GPIO. I have shared all the details in the link below and it can be helpful.

The same code is also available in the git bucket .

Regards,

Anil.

Hi Anil,

Use the project provided by the link:

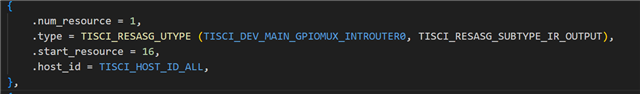

manually modifying the routing for GPIO-16 within the file sciclient_defaultBoardcfg_rm.c,

compiled the updated sciclient_defaultBoardcfg_rm.c file.

Subsequently, I recompiled the SBL with this revised board configuration.

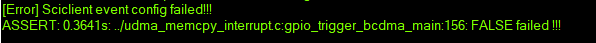

However, the results did not meet expectations.

Regards

Ryan

Hello Ryan,

I assume that you have not done the changes below in your test method , and please confirm.

1. After adding a new entry to sciclient_defaultBoardcfg_rm file for routing 16th Router output to GPIO MUX ROUTER,

did you change a new entry size ?

Please check the below image.

After adding entries, we need to increase the resasg_entries_size value to +1.

For example, by default, this value was 180, and you added a new entry, then you need to change it to 181.

2. After compilation, you need to flash the updated SBL and, if not, please flash the updated SBL on the SOC.

Recently , I have enabled PSRAM + DMA and see if this helps for you and not enabled DMA triggers with the GPIO.

gpmc_psram_io_am64x-evm_r5fss0-0_nortos_ti-arm-clang.zip

Regards,

Anil.