I have a question about the maximum value of overshoot and undershoot on IO pins.

In the datasheet of the component is defined a value of "steady-state max voltage" that must be between -0.3V and "IO supply voltage "+0.3V.

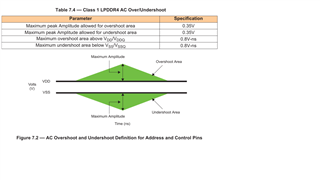

A value for "transient overshoot and undershoot at IO pin" is given below. This value is 0.2xVDD. The maximum time should be 20% of the signal period.

On the other hand, the value of VDDSHVx must be between +1.71V and +1.89V.

Now, if VDDSHVx is +1.71V, the transient undershoot cannot be less than -0.342V for 20% of the signal period. However, it can remain indefinitely at -0.300V indefinitely. Is this correct?

Does the maximum undershoot value depend on the supply voltage itself?

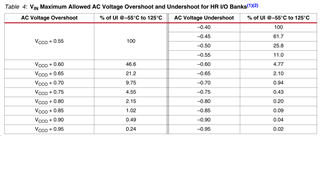

For other devices (e.g. FPGA) the manufacturer usually provides a table that relates the undershoot voltage to the percentage of the signal period. Does Texas Instruments provide such a table?

Regards