Nice to meet you.

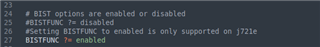

We encountered some issues while using SDK 8.6.

After completing the BIST of MSMC, during the ECC process of enabling MSMC, the RAT mapping ECC aggregator returned a failure.

How should this problem be solved? Please help investigate.

Thank you.

Here are some information:

Enable BIST information and enable ECC of MSMC to return failure when calling function CSL_ratConfigRegionTranslation

__attribute((section(".my_aggr_reg"))) uint8_t mappedEccRegs[0x400];

__attribute((section(".my_aggr_reg1"))) uint8_t mappedEccRegs1[0x400];

__attribute((section(".my_aggr_reg2"))) uint8_t mappedEccRegs2[0x400];

__attribute((section(".my_aggr_reg3"))) uint8_t mappedEccRegs3[0x400];

__attribute((section(".my_aggr_reg4"))) uint8_t mappedEccRegs4[0x400];

__attribute((section(".my_aggr_reg5"))) uint8_t mappedEccRegs5[0x400];

__attribute((section(".my_aggr_reg6"))) uint8_t mappedEccRegs6[0x400];

__attribute((section(".my_aggr_reg7"))) uint8_t mappedEccRegs7[0x400];

__attribute((section(".my_aggr_reg8"))) uint8_t mappedEccRegs8[0x400];

__attribute((section(".my_aggr_reg9"))) uint8_t mappedEccRegs9[0x400];

void* SDL_addrTranslate(uint64_t addr, uint32_t size)

{

void * ret = (void *)(-1);

CSL_RatTranslationCfgInfo translationCfg;

uint32_t transAddr = (uint32_t)(-1);

uint32_t index = 0;

bool result;

if ((addr == SDL_COMPUTE_CLUSTER0_C71SS0_PBIST_BASE) ||

(addr == SDL_COMPUTE_CLUSTER0_A72SS0_PBIST0_BASE) ||

(addr == SDL_C66SS0_VBUSP_CFG_PBISTCFG_BASE) ||

(addr == SDL_C66SS1_VBUSP_CFG_PBISTCFG_BASE) ||

(addr == SDL_COMPUTE_CLUSTER0_MSMC_PBIST_BASE) ||

(addr == SDL_COMPUTE_CLUSTER0_MSMC_PBIST_BASE))

{

/* Disable RAT translation */

result = CSL_ratDisableRegionTranslation((CSL_ratRegs *)PBIST_RAT_CFG_BASE,

PBIST_RAT_REGION_INDEX);

transAddr = (uint32_t)0x60000000;

index = PBIST_RAT_REGION_INDEX;

}

else

{

/* Currently, below aggregators configuration registers can be

* mapped by this code. To expand to other aggregators, additional

* instances of "mappedEccRegs" are needed and should be mapped to

* those additional aggregators. */

switch(addr)

{

case SDL_COMPUTE_CLUSTER0_MSMC_ECC_AGGR0_BASE:

transAddr = (uint32_t)mappedEccRegs;

a = 1;

index = 1;

break;

case SDL_COMPUTE_CLUSTER0_MSMC_ECC_AGGR1_BASE:

transAddr = (uint32_t)mappedEccRegs1;

index = 2;

break;

case SDL_COMPUTE_CLUSTER0_MSMC_ECC_AGGR2_BASE:

transAddr = (uint32_t)mappedEccRegs2;

index = 3;

break;

case SDL_COMPUTE_CLUSTER0_A72SS0_COMMON_ECC_AGGR_BASE:

transAddr = (uint32_t)mappedEccRegs3;

index = 4;

break;

case SDL_COMPUTE_CLUSTER0_A72SS0_CORE0_ECC_AGGR_BASE:

transAddr = (uint32_t)mappedEccRegs4;

index = 5;

break;

case SDL_COMPUTE_CLUSTER0_A72SS0_CORE1_ECC_AGGR_BASE:

transAddr = (uint32_t)mappedEccRegs5;

index = 6;

break;

case SDL_COMPUTE_CLUSTER0_ECC_AGGR_VBUS_BASE:

transAddr = (uint32_t)mappedEccRegs6;

index = 7;

break;

case SDL_COMPUTE_CLUSTER0_ECC_AGGR_CTL_BASE:

transAddr = (uint32_t)mappedEccRegs7;

index = 8;

break;

case SDL_COMPUTE_CLUSTER0_ECC_AGGR_CFG_BASE:

transAddr = (uint32_t)mappedEccRegs8;

index = 9;

break;

case SDL_COMPUTE_CLUSTER0_C71SS0_ECC_AGGR_BASE:

transAddr = (uint32_t)mappedEccRegs9;

index = 10;

break;

default:

break;

}

}

if (transAddr != (uint32_t)(-1))

{

/* Add RAT configuration to access address > 32bit address range */

translationCfg.translatedAddress = addr;

translationCfg.sizeInBytes = size;

translationCfg.baseAddress = transAddr;

/* Set up RAT translation */

result = CSL_ratConfigRegionTranslation((CSL_ratRegs *)PBIST_RAT_CFG_BASE,

index, &translationCfg);

if (result == (bool)true ) {

ret = (void *)transAddr;

}

}

return ret;

}