Other Parts Discussed in Thread: TMS320C6655, TMS320C6652

Hello,

we have used this DSP over several designs. On a new design we are trying to debug the DSP in some situations getting stuck where BOOTCOMPLETE signal is at 0 and not 1. We are following the IO before core sequencing circuit in your datasheet. After the power stablizes and clocks are assweted we always deassert RESET, PORn, and RESETFULLn in that sequence.

Reset is deasserted first, then 2 ms later POR and then 100 uS later RESETFULL

We follow this logic on a a power up or if our microprocessor wants to reset the DSP. We then load the IBL via the I2C EEPROM. This resetting mechanim has worked over several designs.

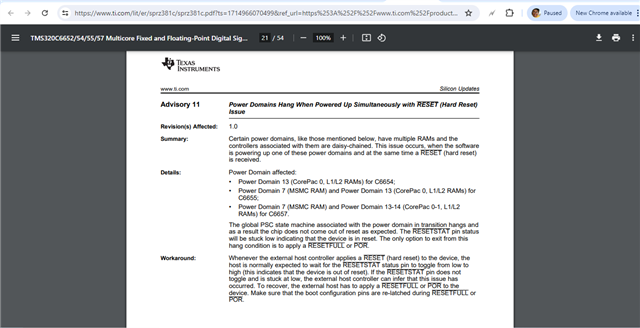

We recently noticed that If we reset the DSP in the middle of the I2C transaction, during IBL transfer, it does not recover and BOOTCOMPLETE is always at 0. Only way to recover is a power cycle. First of all we are trying to understand why this is the case. We cannot rely on a power cycle and would like to fix this.

Thanks,

Divakar