Other Parts Discussed in Thread: TDA4VH

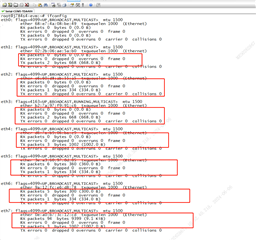

How to evaluate 8 Ethernet Port of CPSW-9G on TDA4VH EVM? Now can evaluate 4 port with 1 pcs of J721EXENETXPANEVM.

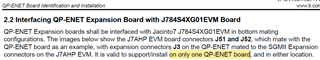

#1. Can we use two pcs of J721EXENETXPANEVM together to evaluate 8 ports?

From the https://www.ti.com/lit/pdf/spruj74 user guide, support only one QP-ENET board.

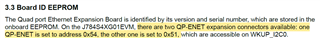

But on later page, two QP_ENET mounted. and has different EEPROM address.

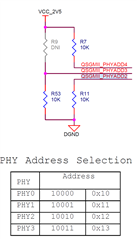

Can we just change PHY address to difference of two ENET board to support 2 at the same time?

#2. I see another k3-j784s4-evm-usxgmii-exp1-exp2.dtso,which should be created for another extension board. but no more information for that.