Other Parts Discussed in Thread: AM1808

Hi,

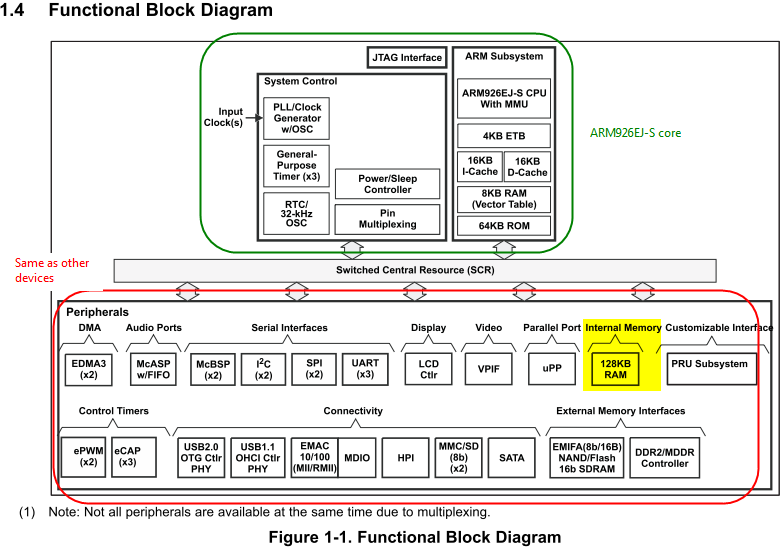

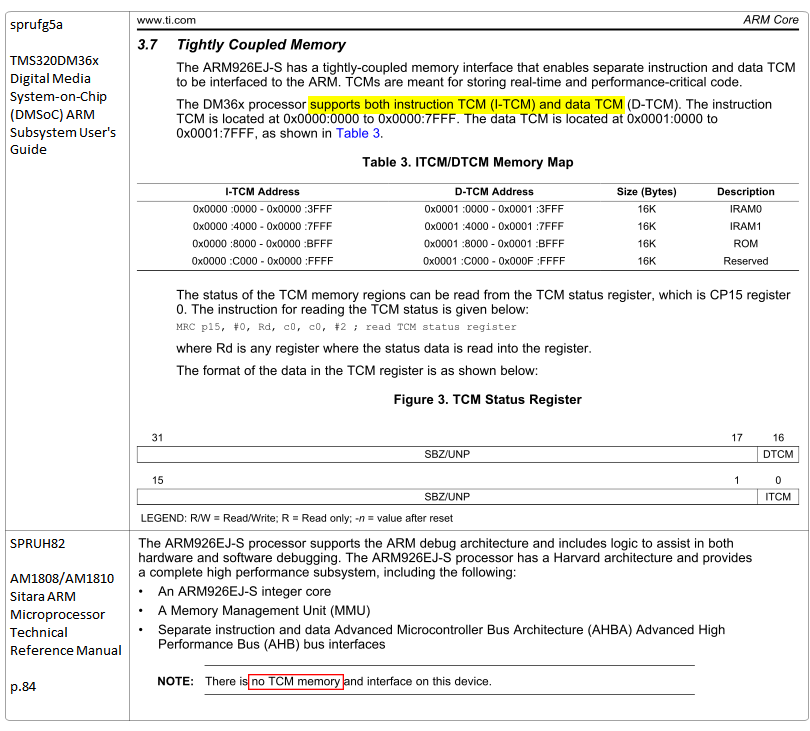

ARM specification defines TCM memory which offers performance similar to cache. With interest on this, I searched keyword TCM in documents of AM1808 and other TI's ARM-based/equipped processors:

The result seems to be:

1. Some have TCM, for example, DM36x

2. Some don't, including AM1808

Is it true? AM1808 just didn't implement TCM?

Zheng