Hi Nick,

By referring to below example, we are able to poll the UART RX for main domain UART using 100us timer.

software-dl.ti.com/.../EXAMPLES_DRIVERS_UART_ECHO_LOW_LATENCY_POLLING.html

I am aware there is no interrupt routed to M4F core for main domain UART.

software-dl.ti.com/.../MAIN_DOMAIN_PERIPHERAL_FROM_MCU.html

But, how about the RX error status for main domain UART ??? In some test cases, I expected an overrun error, but the code below does not seem to flag that.

Also, shouldn't be the "Read and throw Erroneous bytes from RxFIFO" code block checks for "while (0 != errorVal)" instead of checking the errorVal with all the error bits set ???

/mcu_plus_sdk_am62x_09_02_00_38/source/drivers/uart/v0/uart.h

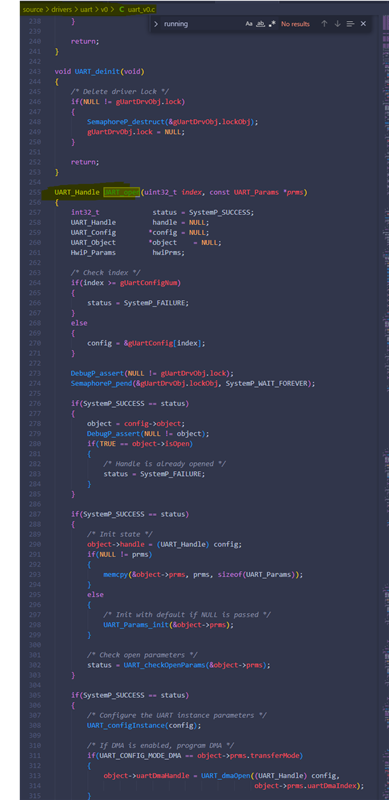

static inline uint8_t UART_getCharFifo(uint32_t baseAddr, uint8_t *readBuf)

{

uint8_t readByte = 0;

uint32_t waitCount = UART_ERROR_COUNT;

uint32_t errorVal;

uint32_t lcrRegValue = 0;

/* Preserving the current value of LCR. */

lcrRegValue = HW_RD_REG32(baseAddr + UART_LCR);

/* Switching to Register Operational Mode of operation. */

HW_WR_REG32(baseAddr + UART_LCR, HW_RD_REG32(baseAddr + UART_LCR)

& 0x7FU);

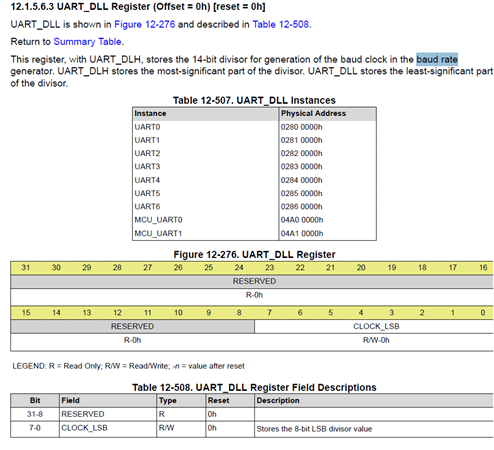

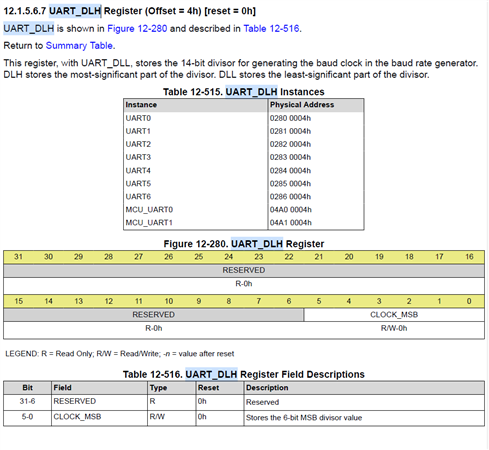

/* Read Rx Error Status */

errorVal = HW_RD_REG32(baseAddr + UART_LSR) &

(UART_LSR_RX_FIFO_STS_MASK |

UART_LSR_RX_BI_MASK |

UART_LSR_RX_FE_MASK |

UART_LSR_RX_PE_MASK |

UART_LSR_RX_OE_MASK);

/* Restoring the value of LCR. */

HW_WR_REG32(baseAddr + UART_LCR, lcrRegValue);

/* Read and throw Erroneous bytes from RxFIFO */

while ((UART_LSR_RX_FIFO_STS_MASK |

UART_LSR_RX_BI_MASK |

UART_LSR_RX_FE_MASK |

UART_LSR_RX_PE_MASK |

UART_LSR_RX_OE_MASK) == errorVal)

{

readByte = (uint8_t) (HW_RD_REG32(baseAddr + UART_RHR) & 0xFFU);

waitCount--;

if (0U == waitCount)

{

break;

}

/* Preserving the current value of LCR. */

lcrRegValue = HW_RD_REG32(baseAddr + UART_LCR);

/* Switching to Register Operational Mode of operation. */

HW_WR_REG32(baseAddr + UART_LCR, HW_RD_REG32(baseAddr + UART_LCR)

& 0x7FU);

/* Read Rx Error Status */

errorVal = HW_RD_REG32(baseAddr + UART_LSR) &

(UART_LSR_RX_FIFO_STS_MASK |

UART_LSR_RX_BI_MASK |

UART_LSR_RX_FE_MASK |

UART_LSR_RX_PE_MASK |

UART_LSR_RX_OE_MASK);

/* Restoring the value of LCR. */

HW_WR_REG32(baseAddr + UART_LCR, lcrRegValue);

}

/* Read non-erroneous byte from RxFIFO */

readByte = (uint8_t) (HW_RD_REG32(baseAddr + UART_RHR) & 0xFFU);

return readByte;

}

rgds,

kc Wong