Hi, TI experts,

How to boot from eMMC boot partition on J721S2 EVM board?

boot flow: SBL HLOS boot

SBL -> u-boot spl -> u-boot.img -> r5 cores/c7x cores, kernel

SDK version is 8.6.

BRs.

Tahm

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi, TI experts,

How to boot from eMMC boot partition on J721S2 EVM board?

boot flow: SBL HLOS boot

SBL -> u-boot spl -> u-boot.img -> r5 cores/c7x cores, kernel

SDK version is 8.6.

BRs.

Tahm

Hi,

By refering to docs/userguide/j721s2/_sources/boot/boot_k3.txt, my steps are as follows:

I am using TI J721S2 EVM Board

0. change the sbl code and open sbl log

1. build the sbl_emmc_img

$(MAKE) -C $(PDK_PATH)/packages/ti/build sbl_lib_emmc_clean BOARD=$(BOARD)

$(MAKE) -C $(PDK_PATH)/packages/ti/build sbl_emmc_boot0_img_clean BOARD=$(BOARD)

$(MAKE) -C $(PDK_PATH)/packages/ti/build sbl_lib_emmc BOARD=$(BOARD)

$(MAKE) -C $(PDK_PATH)/packages/ti/build sbl_emmc_boot0_img BOARD=$(BOARD)

mkdir -p $(VISION_APPS_PATH)/out/sbl_combined_bootfiles

cp $(PDK_PATH)/packages/ti/boot/sbl/binary/$(BOARD)/emmc_boot0/bin/sbl_emmc_boot0_img_$(SBL_CORE)_release.tiimage $(VISION_APPS_PATH)/out/sbl_combined_bootfiles/tiboot3_emmc.bin

2. copy tiboot3_emmc.bin to SD card BOOT partition

3. BOOT from SD card, and promt into u-boot command line:

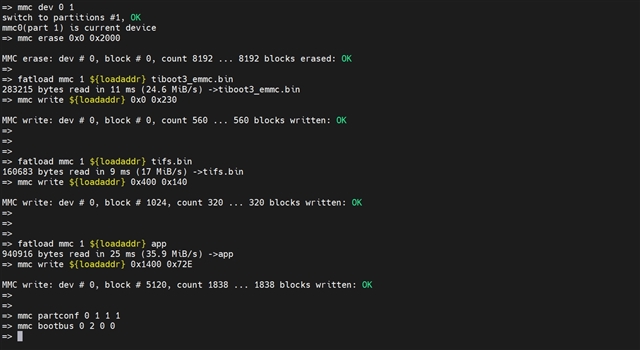

mmc dev 0 1

mmc erase 0x0 0x2000

fatload mmc 1 ${loadaddr} tiboot3_emmc.bin

mmc write ${loadaddr} 0x0 0x400

mmc partconf 0 1 1 1

mmc bootbus 0 2 0 0

4. change the boot mode switch

5. and reboot the board, there is no output from the MCU uart console

Am I missed or did some wrong steps?

BRs

Tahm

Hi Tahm

You just flashed the sbl to the emmc how about the tifs.bin ?

can you follow the steps mentioned in sdk documentation.

Regards

Diwakar

Hi. Diwakar,

Thanks for your response.

You just flashed the sbl to the emmc how about the tifs.bin ?

can you follow the steps mentioned in sdk documentation.

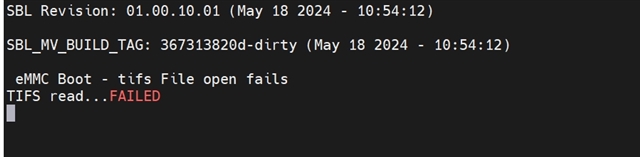

I can see the log from MCU UART console.

it prompts me that tifs read failed

BRs

Tahm

Hi, Diwakar,

By doing below modification in component.mk, the macro EMMC_BOOT0 and MAX_APP_SIZE_EMMC can be passed to sbl_emmc.c

and the sbl seems running

SBL Revision: 01.00.10.01 (May 18 2024 - 13:49:56) SBL_MV_BUILD_TAG: 7948f165a1-dirty (May 18 2024 - 13:49:56) TIFS ver: 8.6.3--1-g2249f (Chill Capybara SCISERVER Board Configuration header population... PASSED Sciclient_setBoardConfigHeader... PASSED Initlialzing PLLs ...done. InitlialzingClocks ...done. Initlialzing DDR ...done. Initializing GTC ...Begin parsing user application Calling Sciclient_procBootRequestProcessor, ProcId 0x20... Calling Sciclient_procBootRequestProcessor, ProcId 0x21... Calling Sciclient_procBootRequestProcessor, ProcId 0x1... Calling Sciclient_procBootRequestProcessor, ProcId 0x2... Calling Sciclient_procBootRequestProcessor, ProcId 0x6... Calling Sciclient_procBootRequestProcessor, ProcId 0x7... Calling Sciclient_procBootRequestProcessor, ProcId 0x8... Calling Sciclient_procBootRequestProcessor, ProcId 0x9... Calling Sciclient_procBootRequestProcessor, ProcId 0x30... Calling Sciclient_procBootRequestProcessor, ProcId 0x31... Calling Sciclient_procBootRequestProcessor, ProcId 0x80... If you don't get the logs of the application while booting from boot0 partition then you might need to pass the MAX_APP_SIZE_EMMC (=<size of you application>) while building your appimage Searching for X509 certificate ...not found Switching core id 8, proc_id 0x1 to split mode... Calling Sciclient_procBootGetProcessorState, ProcId 0x1... Sciclient_procBootSetProcessorCfg, ProcId 0x1, enabling split mode... Calling Sciclient_procBootGetProcessorState, ProcId 0x1... Enabling MCU TCMs after reset for core 8 Disabling HW-based memory init of MCU TCMs for core 8 Sciclient_procBootSetProcessorCfg update TCM enable/disable settings... Copying 0x40 bytes to 0x41010000 Copying 0x490 bytes to 0x41010040 Copying 0x448 bytes to 0x410104d0 Copying 0x318 bytes to 0x41010918 Copying 0x118 bytes to 0x41010c30 Copying 0x8c bytes to 0xa0100000 Copying 0x1184 bytes to 0xa056c300 Copying 0x2400 bytes to 0xa056d488 Copying 0x22ed0 bytes to 0xa05b5f10 Copying 0xa110 bytes to 0xa05e5200 Copying 0x41b8 bytes to 0xa05f7310 Setting entry point for core 8 @0x41010000 Copying 0x61830 bytes to 0x9e800000 Only load (not execute) image @0x9e800000 Copying 0x440f4 bytes to 0x80080000 Only load (not execute) image @0x80080000 Sciclient_pmSetModuleState On, DevId 0x4... Copying 0xabc0 bytes to 0x70000000 Setting entry point for core 0 @0x70000000 Sciclient_procBootReleaseProcessor, ProcId 0x20... Sciclient_procBootReleaseProcessor, ProcId 0x21... Sciclient_procBootReleaseProcessor, ProcId 0x1... Sciclient_procBootReleaseProcessor, ProcId 0x2... Sciclient_procBootReleaseProcessor, ProcId 0x6... Sciclient_procBootReleaseProcessor, ProcId 0x7... Sciclient_procBootReleaseProcessor, ProcId 0x8... Sciclient_procBootReleaseProcessor, ProcId 0x9... Sciclient_procBootReleaseProcessor, ProcId 0x30... Sciclient_procBootReleaseProcessor, ProcId 0x31... Sciclient_procBootReleaseProcessor, ProcId 0x80... Calling Sciclient_procBootRequestProcessor, ProcId 0x1... Sciclient_procBootSetProcessorCfg, ProcId 0x1, EntryPoint 0x41010000... Sciclient_pmSetModuleClkFreq, DevId 0x11c @ 1000000000Hz... Copying first 128 bytes from app to MCU ATCM @ 0x0 for core 8 Calling Sciclient_procBootRequestProcessor, ProcId 0x2... Skipping Sciclient_procBootSetProcessorCfg for ProcId 0x2, EntryPoint 0xfffffffe... Calling Sciclient_procBootRequestProcessor, ProcId 0x1...

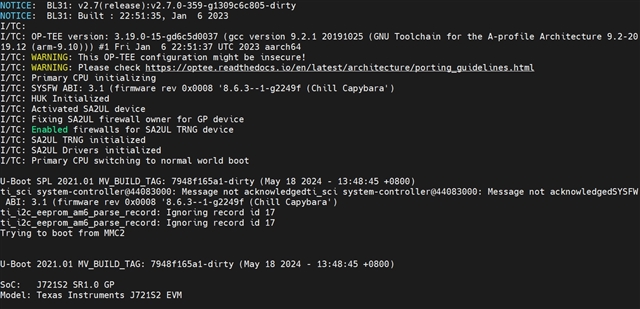

but I can not see any log from the SOC UART

Our BOOT flow is SBL HLOS boot: SBL -> APP (the app contains the data of mcu1_0, bl31.bin, bl32.bin, u-boot.spl)

and then the u-boot.spl boot the u-boot.img.

In the normal case, we can see the log of bl31.bin and bl32.bin in SoC UART

In addition, I found that the sector offset of u-boot.img in eMMC is also 0x1400, which conflicts with the app img. However, we have not seen the logs of optee and atf, so we have not modified the sector offset of u-boot for now.

Do I need to make any other modifications to make the system work properly?

BRs.

Tahm