Hi TI

After repeated hibernation wake up tests, our functional safety has a probability of reporting CLEC interrupt unhandled fault.

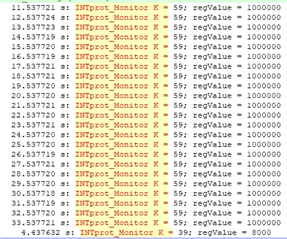

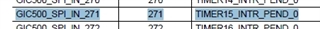

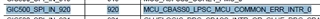

After investigation, the two interrupts are shown in the figure below:

Our CLEC interrupt unhandled fault detection mechanism is to poll the CLEC_EFR_k register,

the polling period is 100ms, if 10 consecutive polling to a certain bit is set, the fault is considered to occur.

I want to know, why repeated sleep wake, there is a probability that these two interrupts are always in the pending state?

Thanks